hi dear supporting team,

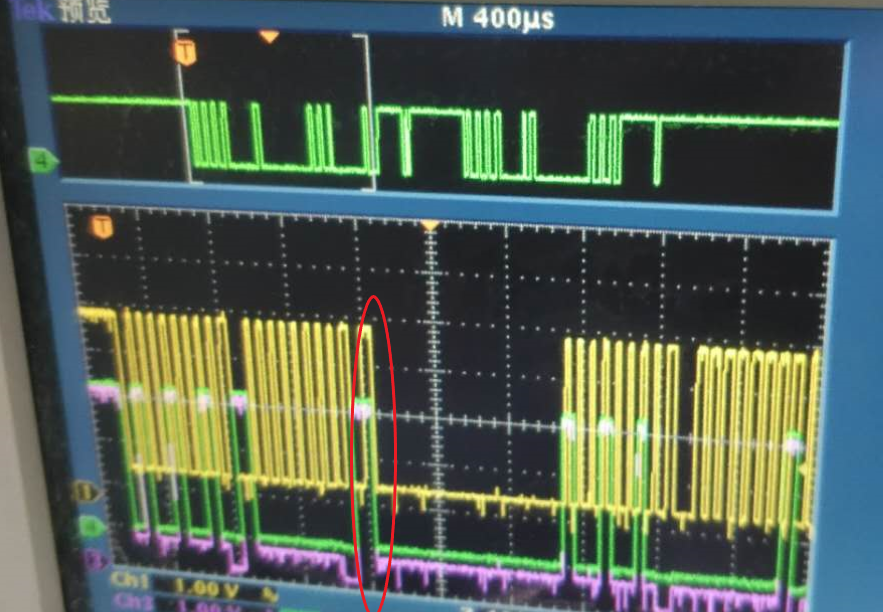

customer is reading temp data from LM75 with address bit set to 001, while in low temp, they will find the read operation was interpreted to write. the timing captured is as below, there are two issue in the timing:

1. the repeat start bit has aligned falling edge with clk (marked in read circle), will this affect the following communication? (the d/s seems has no requirement on the timing)

2. after repeat start, customer will write 0x93 to readout, but in the bus, we could only see 0x92, which seems turn it into write. (we are double check whether the last read bit is pulled to GND by LM75 which turn it to write)

so pls help on question #1 to see what's the exact requirement. tks a lot!