Hello,

I have recently configured an STM32L432 processor to communicate with the PGA411 IC via SPI to get angle information from a resolver. With the FAULTRES pin held low, I am able to receive angle information, write and read to registers, and unlock and save data to the EEPROM.

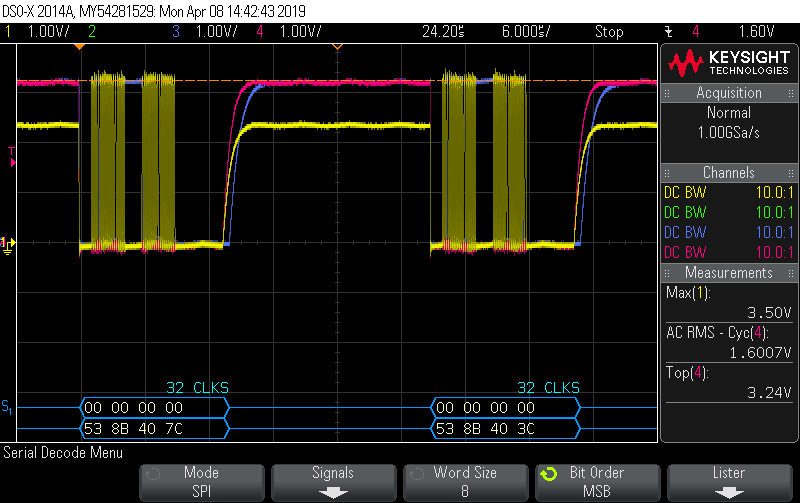

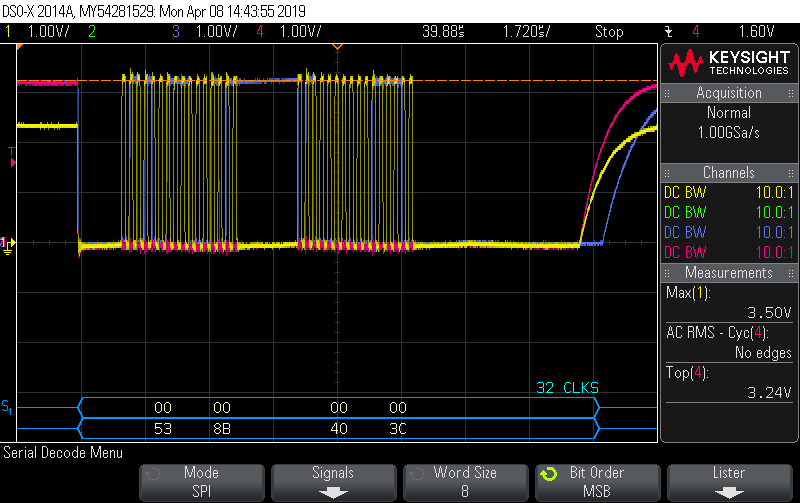

Now to the point where I would like to troubleshoot any other PGA411 faults, I have set the FAULTRES pin high. All system functions appear to be operating fault free, including SPI register writes, except for when I perform a SPI register read. Every attempt at reading a register, I receive a SPI_ERR fault of 0x1, which is an an invalid CRC or SPI clock. The interesting thing is that I do always receive the correct data from the registers when reading.

Does anyone have any ideas for what could be causing an error like this? For example, a simple read process of mine for OVUV1 looks like this:

- Set transmit data to be written to 0x5300000B. Read address = 0x53, dummy data = 0x0000, CRC-6 = 0x0B

- Transmit data over SPI

- Second transmit over SPI, same data, sent 50us later

- Store received data

There is no specification for what the dummy data contents are correct? Do any OVUVx registers require the device to be in diagnostic mode to read?

Let me know if there is any other information I can supply that could help diagnose this.

Thank you