Other Parts Discussed in Thread: TIDEP-0091, IWR1443

Hi champion,

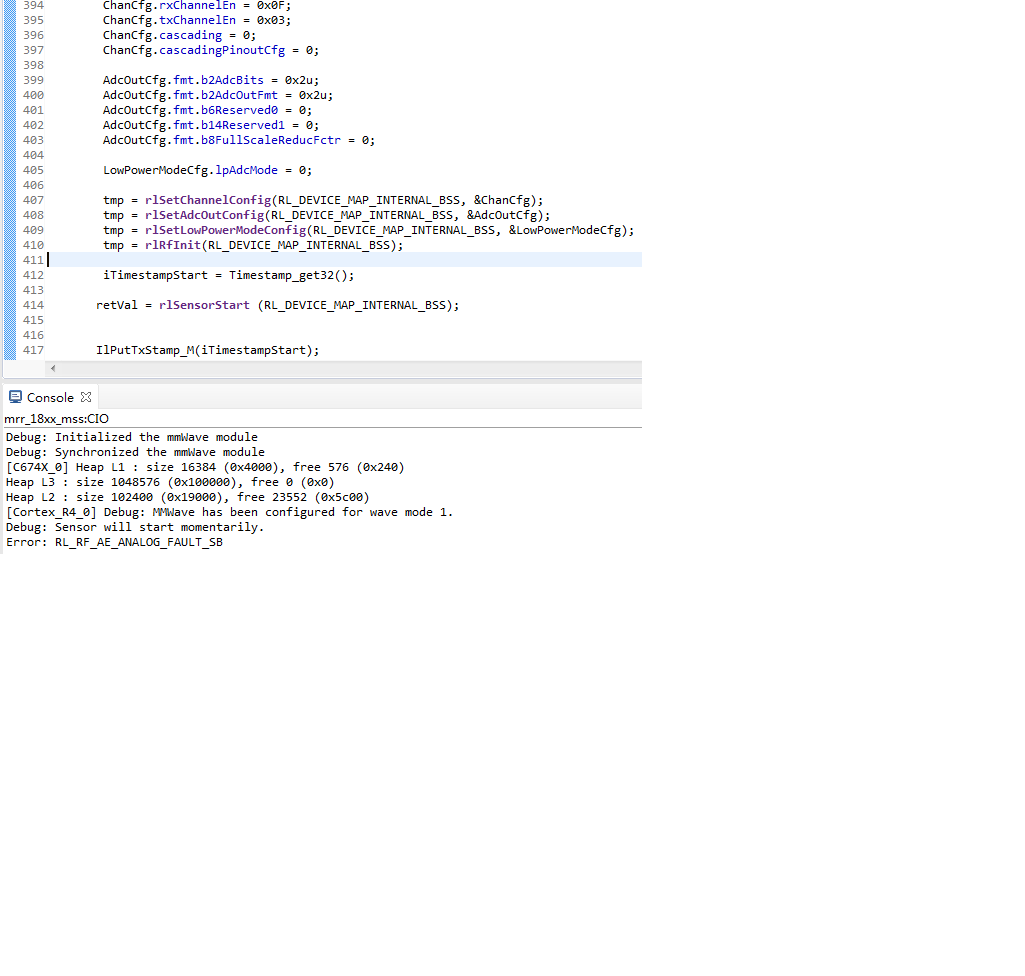

Customer want to turn off Tx and Rx channels in inter-frame idle period to save power. They tried to call rlSetChannelConfig, but find after they open the channels in the next frames, the ADC data is all zero.

Could you help to check is there any way to reduce the power in inter-frame period? Can we close the Tx and Rx channel in this period?

Thanks,

Adam