Other Parts Discussed in Thread: FDC1004, FDC2112

Hi Team,

Supporting a customer with FDC2214 designed in.

Looking at the datasheet Figure 16 and 17, these parts seem to only support a write-read style transfer rather than a direct read, which is unfortunate since the extra two bytes of the transfer seem to limit practical performance a bit. And it also seems to contradict the documentation for the 211x chips. They also do not seem to allow for multi-register reads.

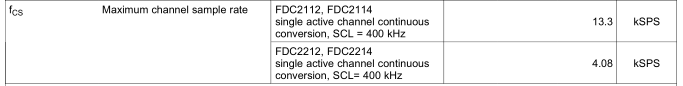

The FDC2214 datasheet claims the following,

That would not possible, since for an I2C write-read, a 5 byte transfer in this case, at 400KHz we could get:

400[1/s]*(1/9)[b/B]*(1/5)[B/transfer]*(1/1)*[transfers/sample] = 8.8 ksamples/second.

However, the documentation claims 13.3 kSPS is possible.

Is there another way to read data from the chip? Attempting a multi-register read just yields a NACK, but perhaps a simple read after issuing the register address once works?

In the case of the 221x chips, it would be great if there was a more efficient way to do this than a write-read for both the MSB and LSB of every sample. In theory, that yields a sample rate of:

400[1/s]*(1/9)[b/B]*(1/5)[B/transfer]*(1/2)*[transfers/sample] = 4.4 ksamples/second.

But that is assuming perfect timing. The customers firmware has a 43-microsecond gap between I2C transfers, and is also servicing both the FDC1004 and FDC2214 on the same bus, which is limiting the sample rate to around a kilohertz. This isn’t terrible, but especially as we use more than one channel, theywould like to get things working as good as possible.

Can feedback to get around this?

Thanks, Joey