I have following queries regarding 1243p cascade system:

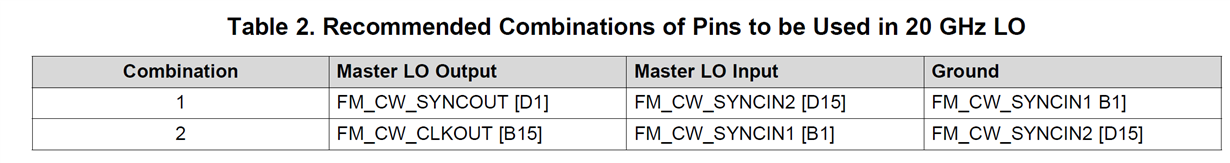

1. For a cascade of 1243p chips, there are 2 master pin configurations as shown in the table. Is there a recommended configuration among the 2 based on some thorough evaluation?

2. For the Power splitter used to distributed LO clock, are there some caveats? Should this be present on the PCB itself or we can hook something up externally?

3. Once the cascade HW is set up, what is right FirmWare to be used with the system?

Thanks