Hello TI

We are developing a gas sensor board and have a need to test our board for general functionality before investing in sensor installation and test. Primary among the functions we are testing is the TIA gain.

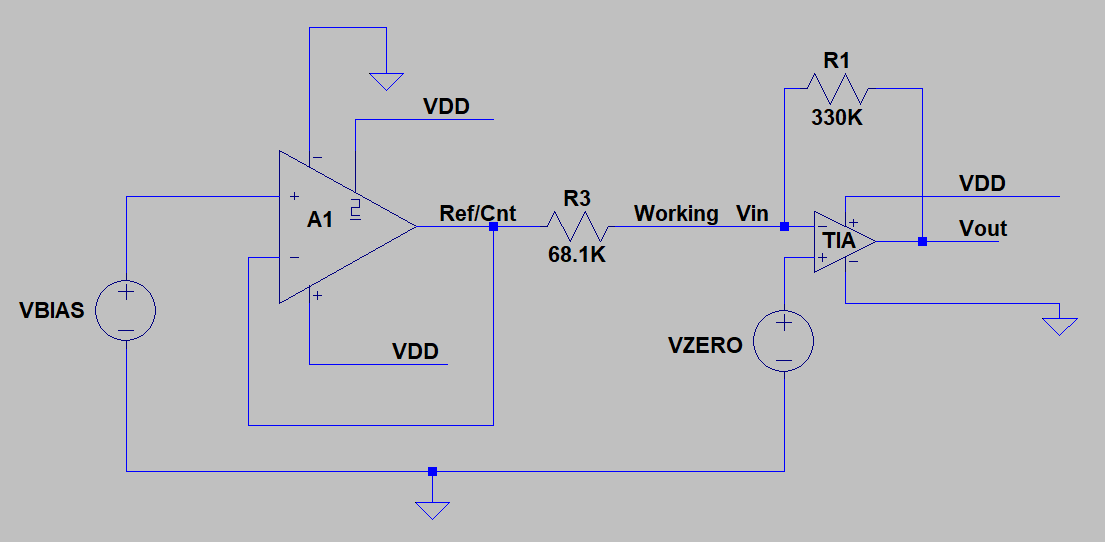

The TIA is configure with an external precision 330k resistor, using positive 20% ref internal zero setting. We have a very simple test that involves shorting the CE and RE pins and placing a precision 68.1K resistor between them and the WE pin. This should allow us to step through the reference bias setting from 0 to 20%, resulting in a "precision" current being injected into the WE pin, to confirm the TiA Gain.

Problem: The apparent TIA gain is changing with the ref bias setting. The value is closer to "correct" at higher bias level and more than 5% high at the lower settings.

I cannot find any specs concerning the 91000 that add up to this level of TIA error.

What can I possibly be missing?

Thank you kindly

Robin A Robinson

Principle engineer,

TANSTAAFL LABS