Other Parts Discussed in Thread: MMWAVE-SDK

Hi MibSPI specialist,

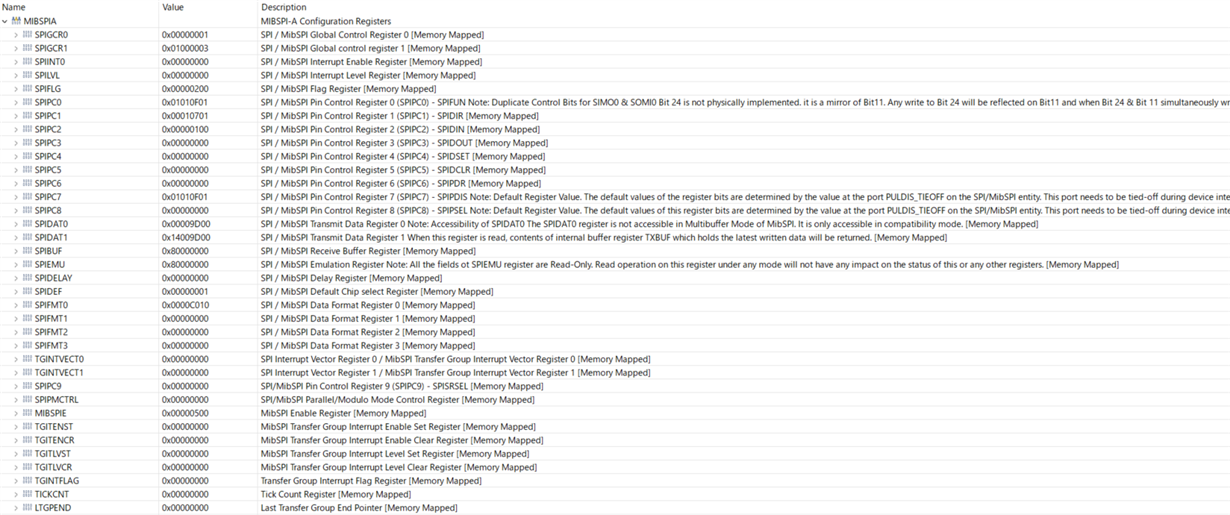

I am facing the problem that MibSPI does not capture Rx data into SPIBUF.

I use SPI mode as a master device, and execute readout operation of slave device (CAN transceiver) ID register.

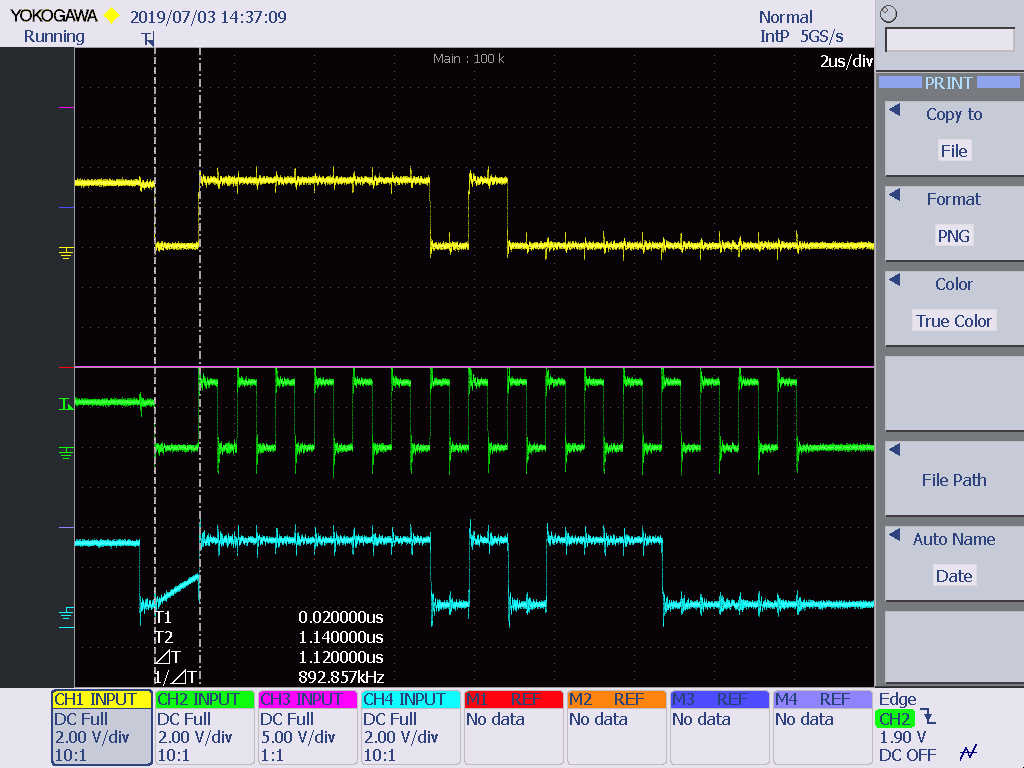

When observing each signal of SCLK, MOSI and MISO with an oscilloscope, it is expected waveform .

However, capturing to SPIBUF is not performed.

RXEMPTY changes from 1 to 0. However, the data is All 0.

I attach a waveform and a register dump.

The waveforms are MOSI, SCLK and MISO from the top signal.

Are there any restrictions?

Best regards,

KH