Other Parts Discussed in Thread: , IWR1443

Hello everyone!

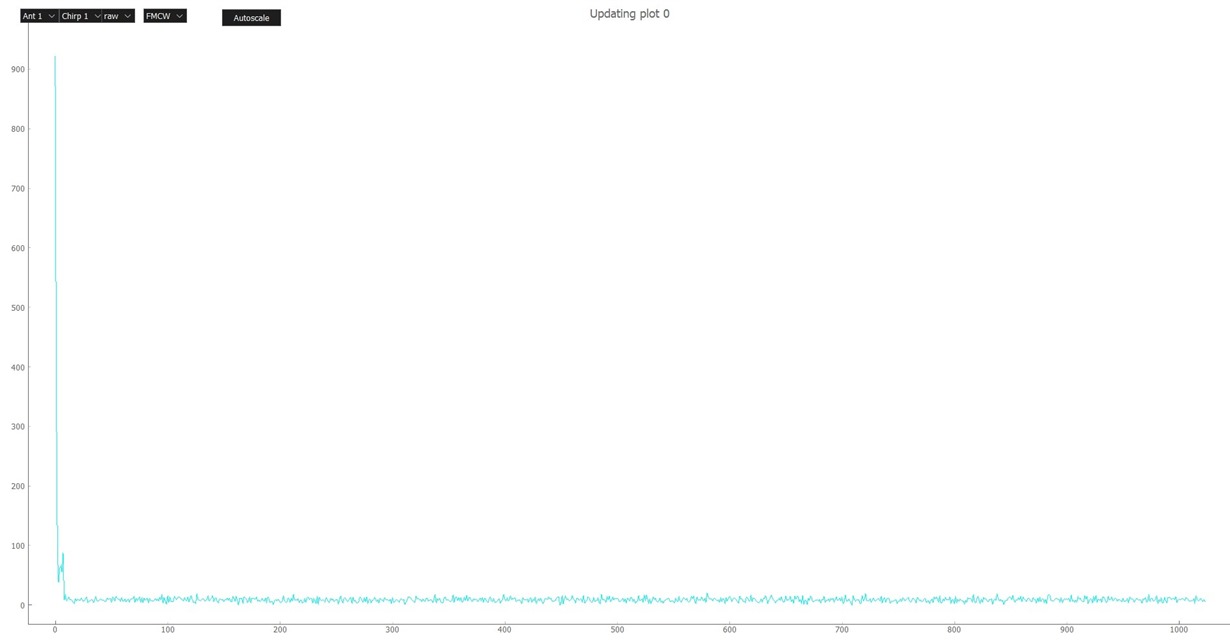

I'm trying to capture FMCW chirps, but for some reason the only thing I can get is this plot (same for all 4 rx antennas and 2 long chirps in configuration).

X axis -- sample number

Y axis -- sqrt(I^2+Q^2)

So, for some reason I got spike on first sample, some samples with abs values in ~50-100 range and tail is Gaussian noise near zero.

I expected sine-like waveform which I can use for further processing. This picture was plotted by script on my PC. Capture chain was simplified to ADC -> eDMA -> DSS L3 (shared with master) -> MSS SPI w/ DMA -> PC, so pretty much everything is done by hardware without the use of CPU resources.

My troubleshooting attempts included: usage of memcpy/memmove instead of eDMA, using UART over SPI (even dumb printfs with data straight from ADC buffer), HSRAM instead of L3. In all cases results were the same. Tested both on custom board and on IWR1642BOOST.

We use custom configuration sequence with mmwavelink and modified cli commands from demo, but this file contains our configuration converted into SDK Demo format.

Any thoughts on what can be wrong with ADC data?

Regards,

Ivan