Other Parts Discussed in Thread: AWR1243

Tool/software: TI C/C++ Compiler

Hello,

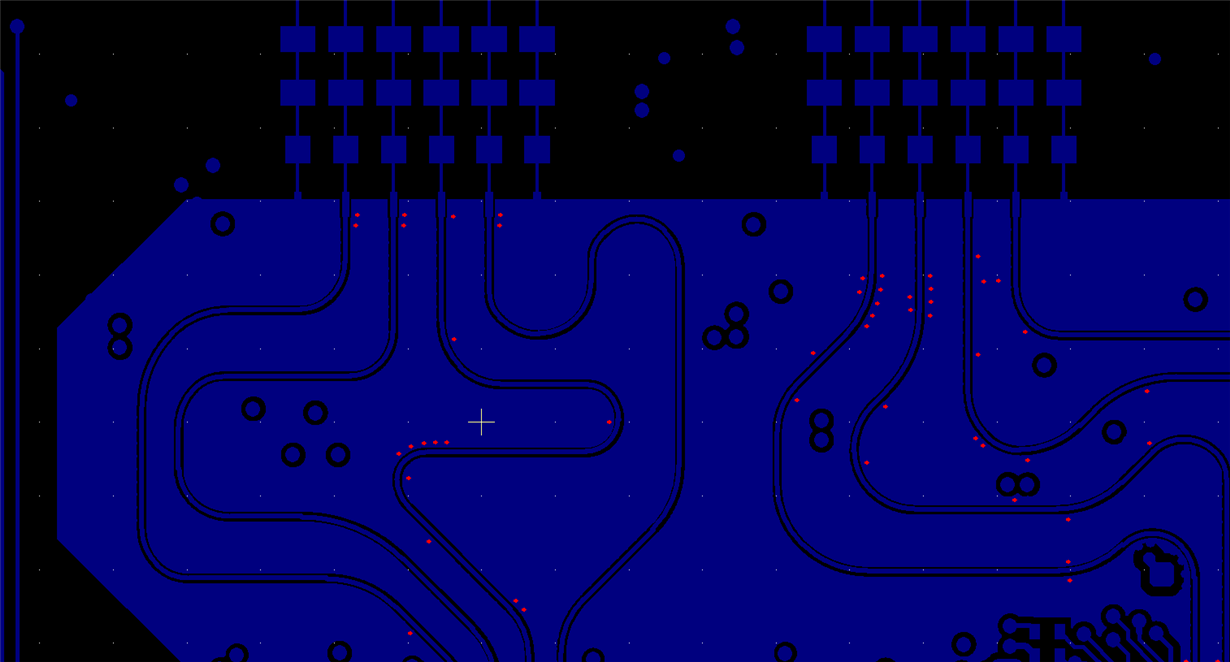

I have a problem about AWR1243 PCB layout. I see in AWR1243BOOST PCB, there are many blind holes around transmitting and receiving antennas from top to layer2. Because the process of blind hole is very expensive, I want to konw if I can use the through hole to replace the blind hole, if it can not , why?

is it possible if all layers under the antenna area are paved GND or keep empty, Is this workable to use the through hole? Can you give me some advice? thanks very much!