Hello

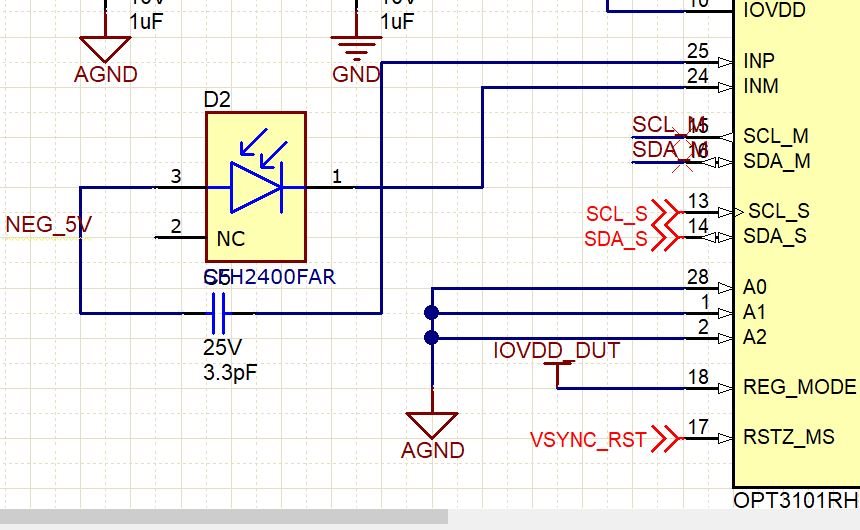

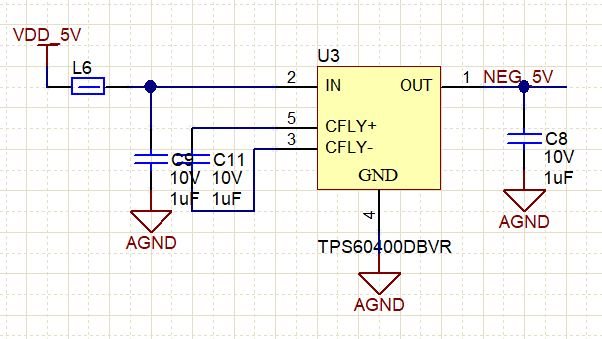

I use photodiode SFH2700 FA and use a capacitor Cpd=5.8pF as matching capacitor on my design, is that ok? on the SFH2700FA datasheet, there is a curve for capacitance vs VR voltage. but how can I choose the matching Cpd value based on the curve?

thanks