Other Parts Discussed in Thread: TDA2

The SDK I used is PROCESSOR_SDK_RADAR_03_07_00_00, I didn't change the code inside, the only modification is:

After compiling, I put the MLO (C:PROCESSOR_SDK_RADAR_03_07_00_00\vision_sdk\binaries\apps\tda2xxx-cascade-radar)

and the AppImage (C:\PROCESSOR_SDK_RADAR_03_07_00_00\vision_sdk\binaries\apps\tda2xx_Cascade_bios_radar\vision_sdk\bin\tda2xx-evm\sbl_boot)

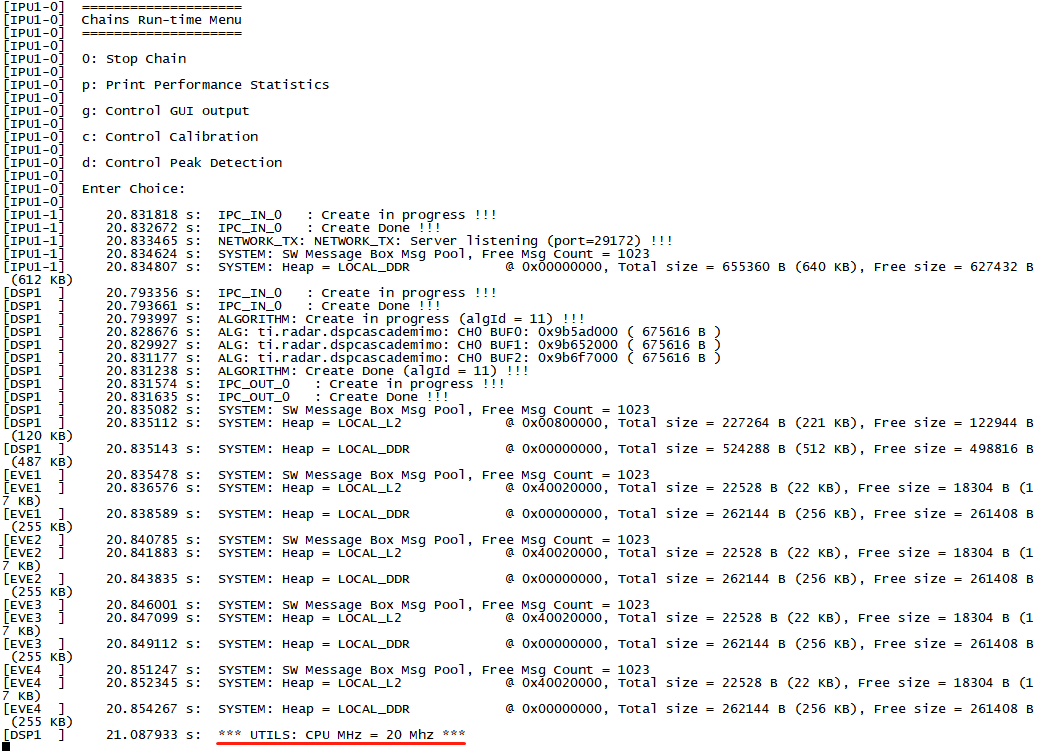

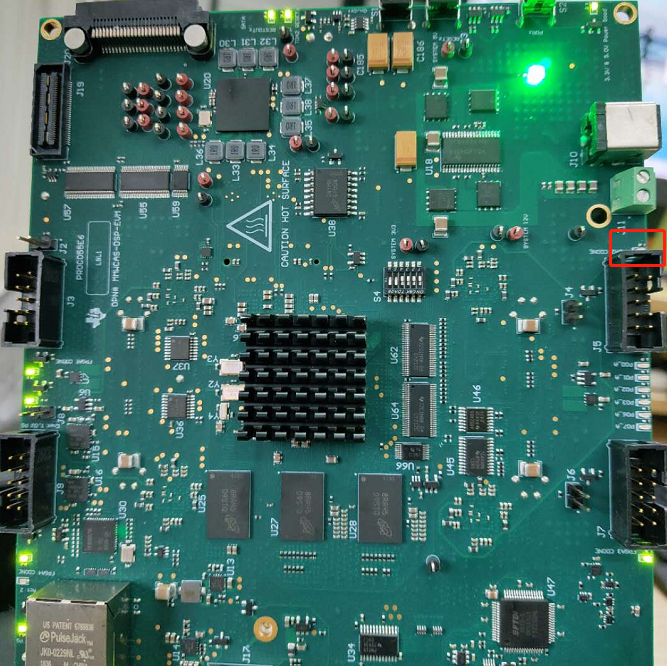

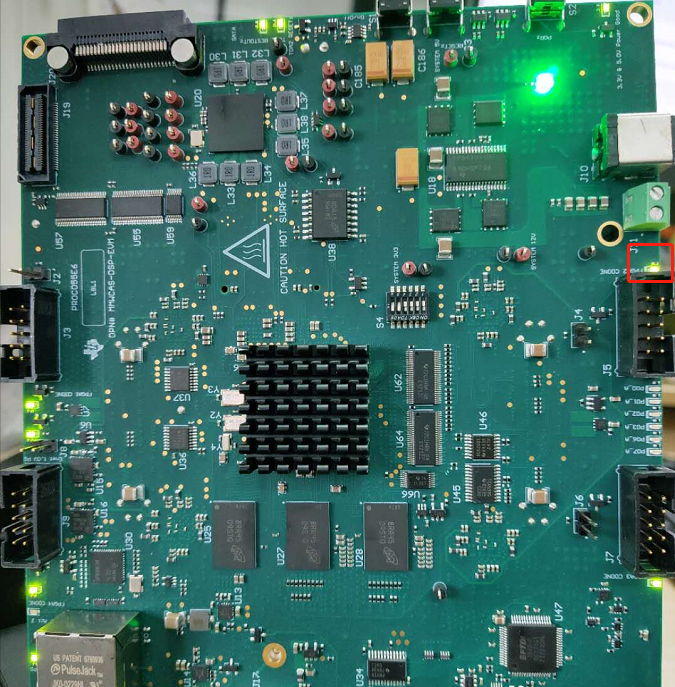

into the SD card and boot.The mode I chose are as follows:

Vision SDK Usecases: 1: RADAR Usecases

RADAR Usecases: a: Cascade RADAR (4 AWR1243) Capture + RADAR Object Detect (DSP) + NetworkTx (TDA2xx Only)

2D FFT Core Selection: 2: EVE

Select Network Mode: 1: TFDTP

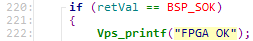

After that, there is a high probability that the last line shown below will not be printed:

At this point, part of the radar code can work normally, but the AlgorithmLink_radarProcessProcess() function in

C: PROCESSOR_SDK_RADAR_03_07_00_00\vision_sdk\apps\SRC\rtos\radar\SRC\alg_plugins\radarprocesslink_algplugin.c

will not be executed, so the radar does not work normally.

If I keep rebooting the radar, eventually

*** UTILS: CPU MHz = 20 MHz ***

will be printed and the radar will working normally.

What should I do to avoid this?

thank you very much

best regards