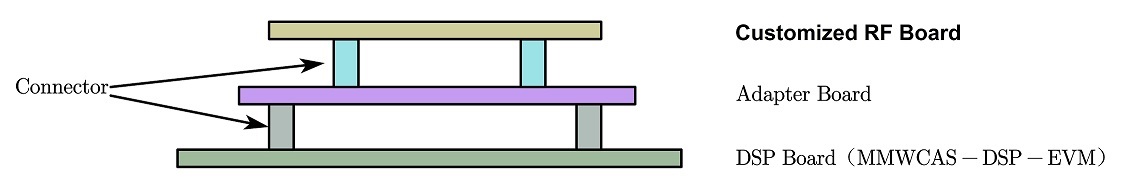

Other Parts Discussed in Thread: TDA2, , MMWCAS-DSP-EVM

Hi,

My customer found when they use TI cascaded EVM to capture ADC raw data, the first frame data is wrong, but the later frames are ok. Why this happed? Is it due to the VIP IO delay setting? If it is true, why the later frame will be correct? Would you pls help to point out me the related code in vision sdk?

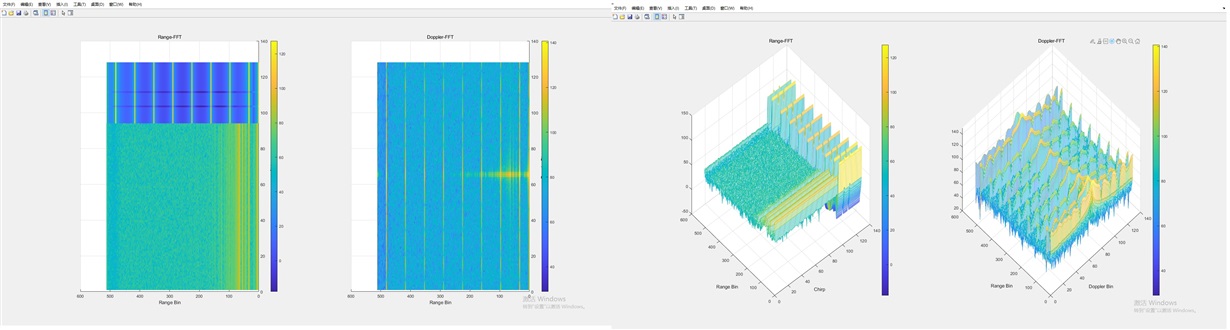

Below is the first issue frame info.