Part Number: PGA411Q1EVM

Hello,

I'm trying to tweak the values of the AFE for the PGA411 and I'm running into some problems.

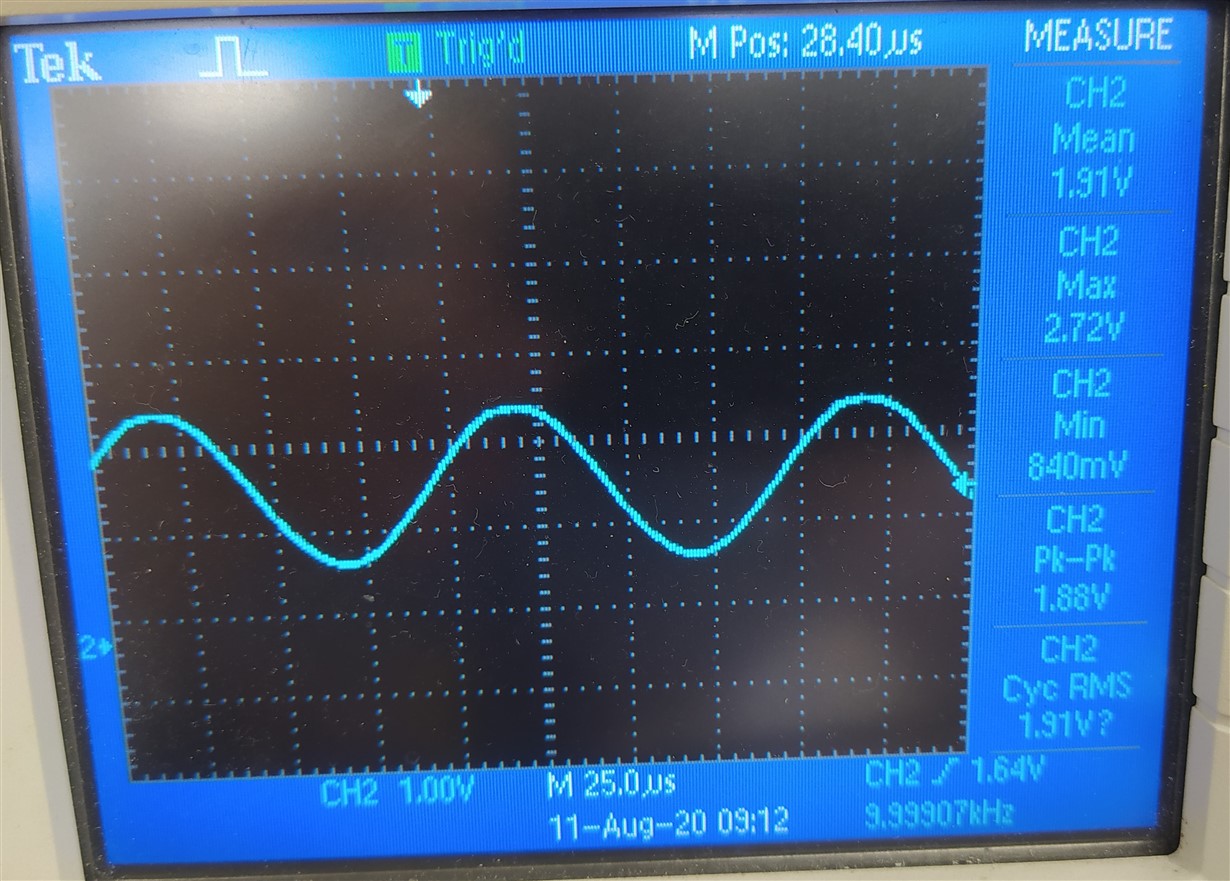

According to the datasheet the VIZx signals should be centered around 0.5*Vcc (2.5V) but in my case this is not true. They are centered around 1.9V. This is making things a little bit complicated because all of the high and low voltage thresholds for all of the fault diagnostics assumes this. I have checked the COMAFE pin and it is indeed 2.5V and I have also checked the OSIN and OCOS signals and they are also centered around 2.5V.

This is a screenshot of one of my VIZx (the rest look the same):

Any ideas why this is happening?