Hi,

I'm developing on a PGA970EVM and can't get the DAC to Output the Voltage, because the FaultDiag value is always set to one which disables writing the value to the output register.

When watching the Memory Registers in the debugger, I instantly get several Diagnostics Errors right after reset:

PSMON1 00000000b (Binary) PSMON1 Fault Detect Register [Memory Mapped]

PSMON2 00010000b (Binary) PSMON2 Fault Detect Register [Memory Mapped]

AFEDIAG 00000000b (Binary) AFEDIAG Register [Memory Mapped]

AFEDIAG1 00110011b (Binary) AFEDIAG1 Register [Memory Mapped]

AFEDIAG3 00110011b (Binary) AFEDIAG3 Register [Memory Mapped]

AFEDIAG4 00110000b (Binary) AFEDIAG4 Register [Memory Mapped]

I always get the exact same Diagnostics Errors.

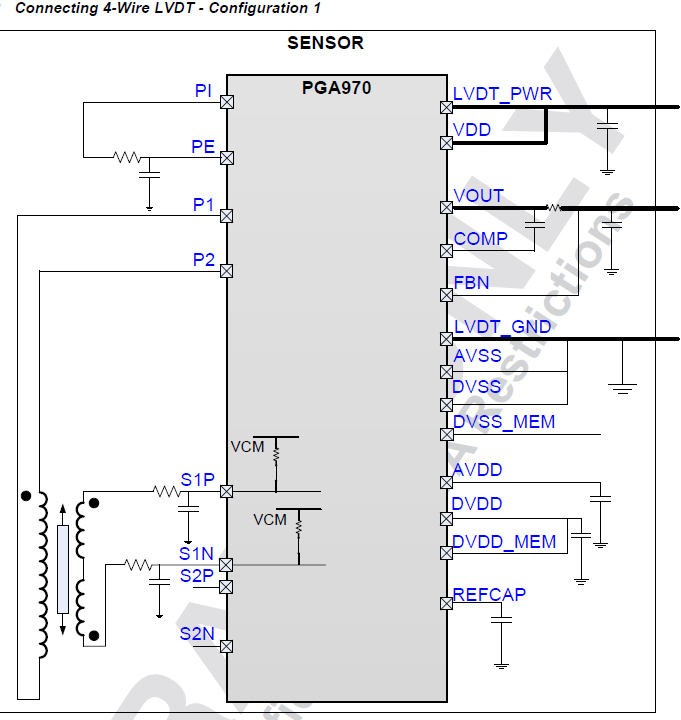

The only things plugged into my EVM are a 12V PSU and a LVDT in 4 Wire Connection like this:

Any Ideas what could cause this or how to resolve this issue?