Other Parts Discussed in Thread: TDC7200, MSP430F5529

Dear ,

I use SPI to communicate with TDC7201.

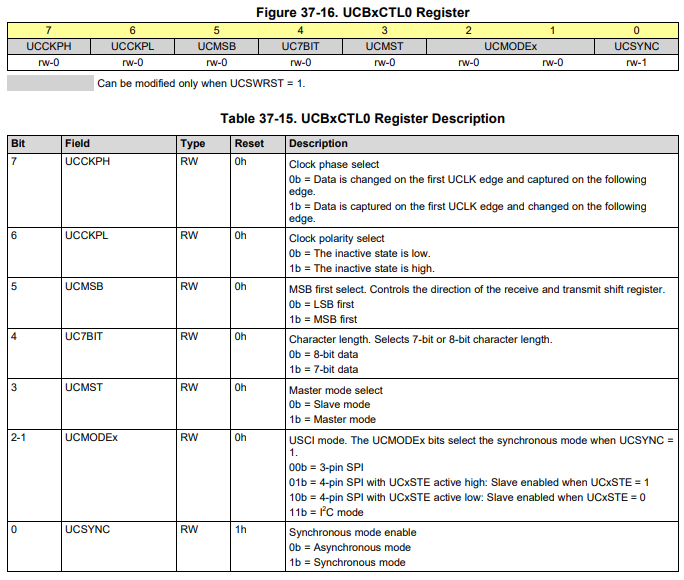

I use SPI Mode 0 CPOL=0, CPHA=0.

16M clock is checked OK. Enable pin is high.

But TDC don't response my read command.

Do you have any reference code ?

I send 0x80, or 0x81.