Other Parts Discussed in Thread: AWR1642

Hello,

What can cause the sensor to miss the frame process deadline ?

I am trying to implement a non-OS version of the MRR project, i have used the MmwaveLink library directly to configure and start the device from the DSS.

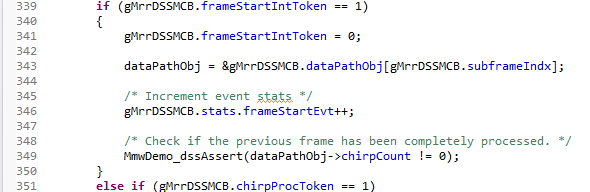

After applying all the MRR configurations and starting the sensor, it always throws the assert error before processing any chirps.

Regards,

Mohamed