Hello everyone,

I'm using the AWR1642 now on the board which designed by ourselves.When i use the software trigger mode,everything works fine.

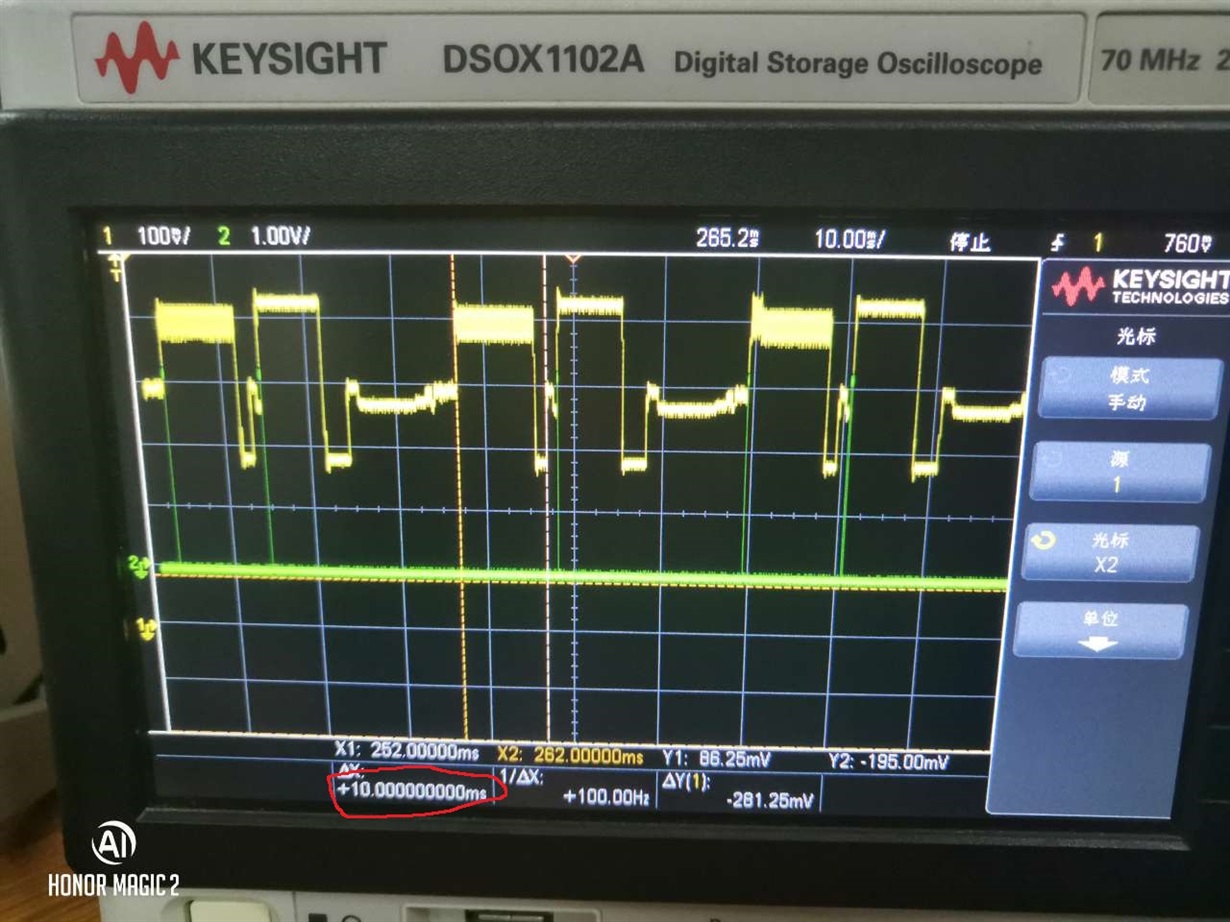

But right now,when I use the hardware trigger mode to start the frame,I noticed that the current was abnormal.I'm using the advanced frame mode.The first and second subframe periodicity both set to 10ms.When I measured the current with an oscilloscope,I noticed that the current was a little high between the end of subframe periodicity and the next hardware trigger pulse(See Figure 1).So, what i want to know is what is the RSS working status like after the end of subframe and before the next hardware trigger pulse?And why does the current abnormally rise up?On the other hand,with the same setup(except the subframe periodicity), there was not that case with software trigger mode.

Best Regards

Dawei Wang