Other Parts Discussed in Thread: TUSS4470, TUSS4440

I try to get sampled data with direct data burst from PGA460. The response is not clear to me. I hope somebody can give me an explanation.

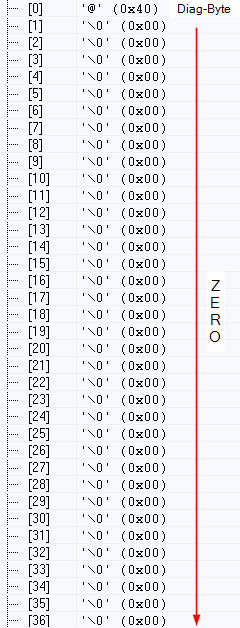

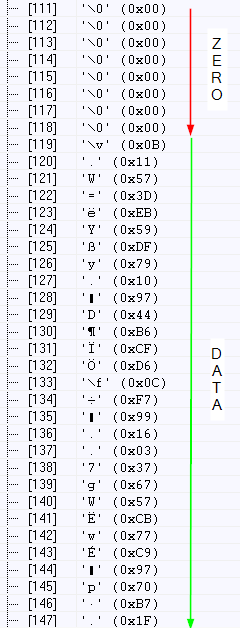

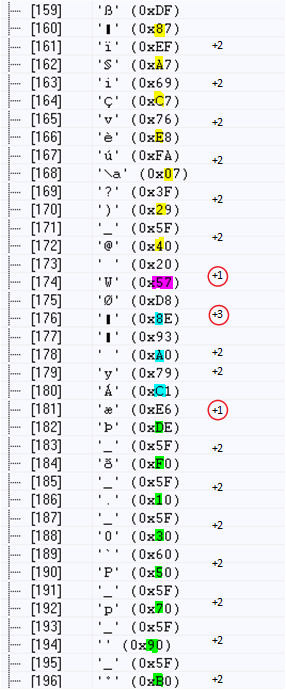

1) The response begins with a DIAG-Byte (0x40) followed by a Number of Null-Bytes. The Count of Null-Bytes varies in response frames from 106 to 124. Should it be a constant count of Null Bytes? Whats the right number of Null-Bytes. In a recent post there was mentioned that null-bytes are sent for about ~120us.

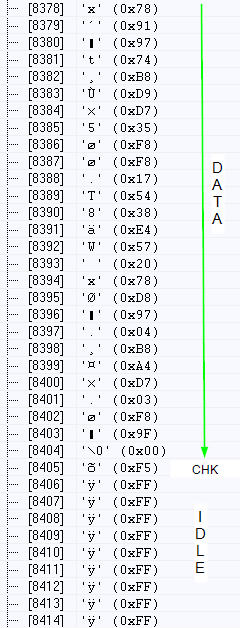

2) The expected number of response frame bytes is 2+payload (diag+payload+chk), where payload = (rec_len+1) *4096. For rec_len = 1 , I would expect 8194 bytes, but pga460 send more bytes until miso gets idle (0xff). Are the initial null-bytes included in payload, or added to payload.

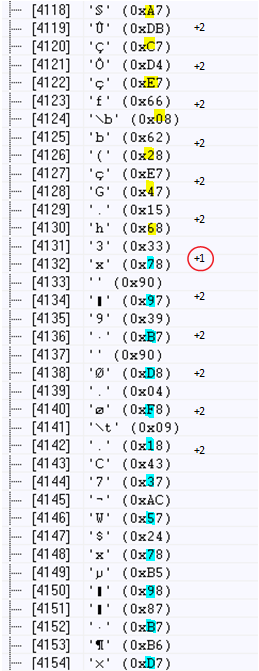

3) Is it possible to get more bytes, when SPI-Master-SCLK is a slightly obove 8MHz. Could this be observed by the sample counter in 12Bit mode?

4) The sample counter in 12bit mode increments by 2. Is this correct ?

5) In a recent post it was mentioned, that a new pga460 with external clock will be released. When ?

Thank you for your response !

Mathias-J