Hello,

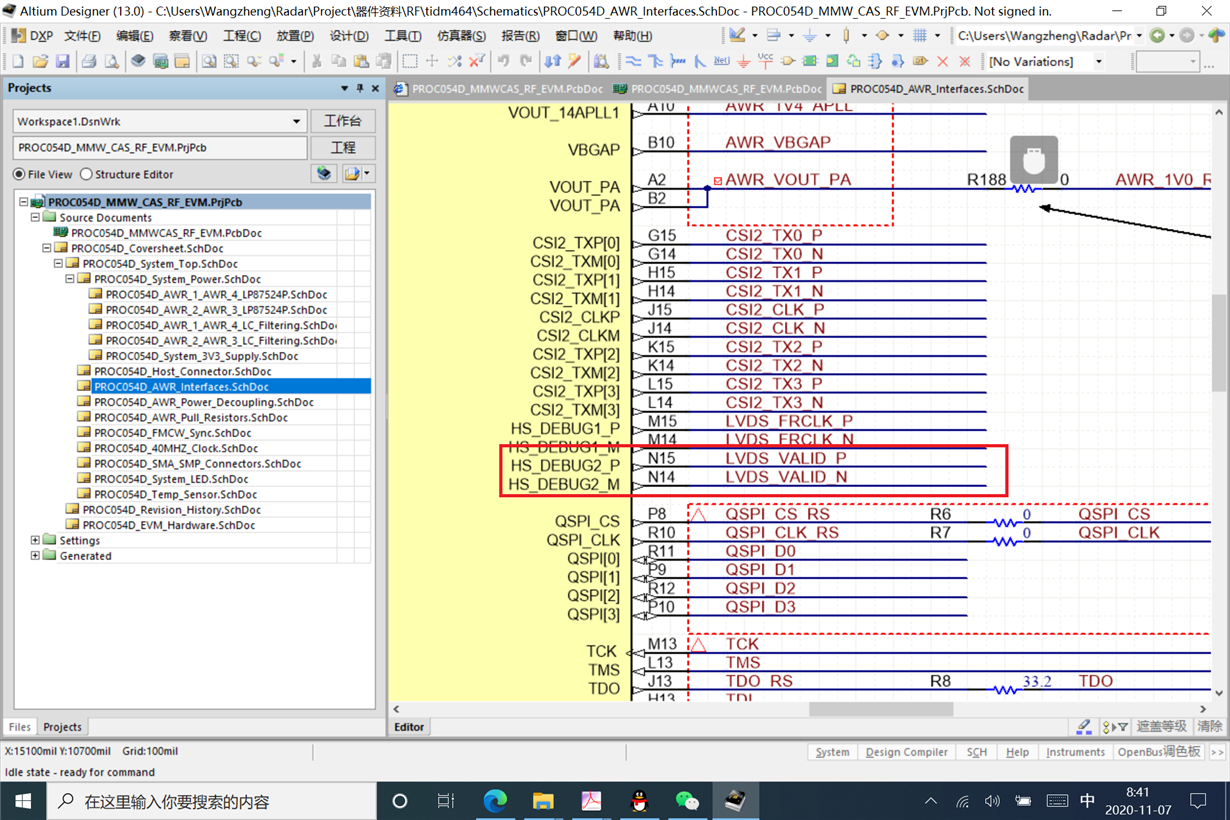

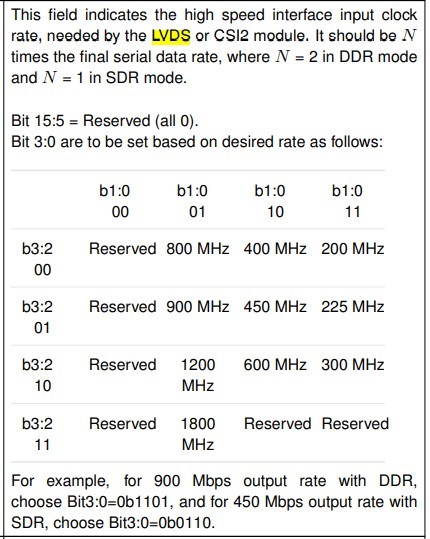

I am designing 4 pcs cascaded radar based on AWR2243+FPGA, LVDS of AWR2243 has 7 pair differential line: from timing datasheet of 2243, I don't see HS_DEBUG2, from reference design, these HS_DEBUG2 is LVDS_valid_P/N, I don't know the function of these two pin, because I/O limited of FPGA, could I don't connect the two pins to I/O of FPGA, that means I only connect clk, 4 pair data, one pair HS_DEBUG1(FRCLK),it effect the data transfer from 2243 to FPGA?