Other Parts Discussed in Thread: AWR1843,

Hi Experts,

We are working on immigrating RX antenna DBF algorithm onto AWR1843's HWA, which simply performs an element-wise complex multiplication over DFFT output and DBF twiddle factor vector (corresponding to RX antenna spacing).

I wrote a test function which generates test pattern on L3 and then copy it to HWA memory using EDMA, and then fill the HWA internal memory using HWA_configRam(), and finally start HWA and wait until complete.

Config code:

Process code:

But the HWA output is always zero if HWA complexMultiply.mode is set to HWA_COMPLEX_MULTIPLY_MODE_VECTOR_MULT,

while if complexMultiply.mode is set to HWA_COMPLEX_MULTIPLY_MODE_MAG_SQUARED, the output meets my expectation.

The main difference is that Magnitude squared mode does not use the HWA internal memory.

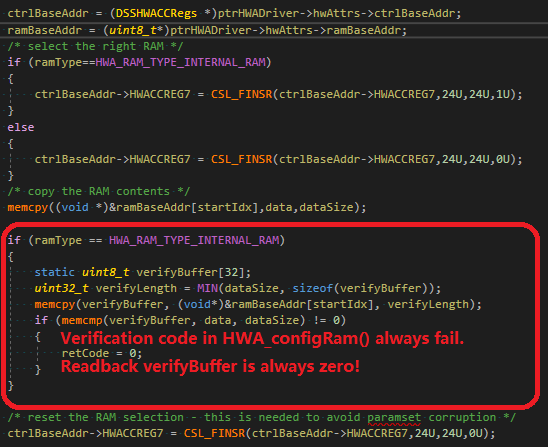

So I checked the configRam and added the code below to make sure that writing to the HWA internal RAM is successful, but the memcmp always fails as the verifyBuffer is always zero, it seems I simply failed to write my twiddle factor vector into the HWA internal memory even though I toggled the 24th bit of HWACCREG7.

My question is:

0. What is the correct programming sequence to start a FFT HWA param with CMULT pre-processing? A demo would be very nice.

1. What is the data width of HWA internal memory which holds CMULT complex vectors? I am assuming a 32*2bit complex vector with lower 21bit valid for both image and real part.

2. Is there a way to validate successful writing to the HWA internal memory? (over JTAG debug? or CPU readback?)