Hey all,

I'm having a pretty big issue in multiple fielded systems containing the PGA411-Q1. What I see is after long power outages, the PGA411-Q1 does not respond to any SPI commands. RESET_N is high. The issue can only be solved by power cycling affected system. There is no SPI communication to the PGA411-Q1 in this failure mode. Cycling RESET_N does not fix the problem. In our application, power cycling the system is very difficult and expensive to do.

I was able to reproduce this in my lab, and found that when this failure happens Vdd is 300mV and Vext stays at Vcc of 5V. This means that the Vext boost regulator is not enabled, and the MCU is stuck in the reset state.

Further investigation shows that with RESET_N being low, the difference between the PGA411-Q1 getting stuck in the reset state and working is how soon Vdd turns on with RESET_N low. If the PGA411-Q1 works, Vdd turns to 1.8V in 4.8ms, if PGA411-Q1 does not work, PGA411-Q1 turns to 300msV in 3.2ms. Note that I said that Vdd is turning on when RESET_N is low. Why is this? Documentation shows that Vdd and Vext both turn on in the diagnostic state when RESET_N is high.

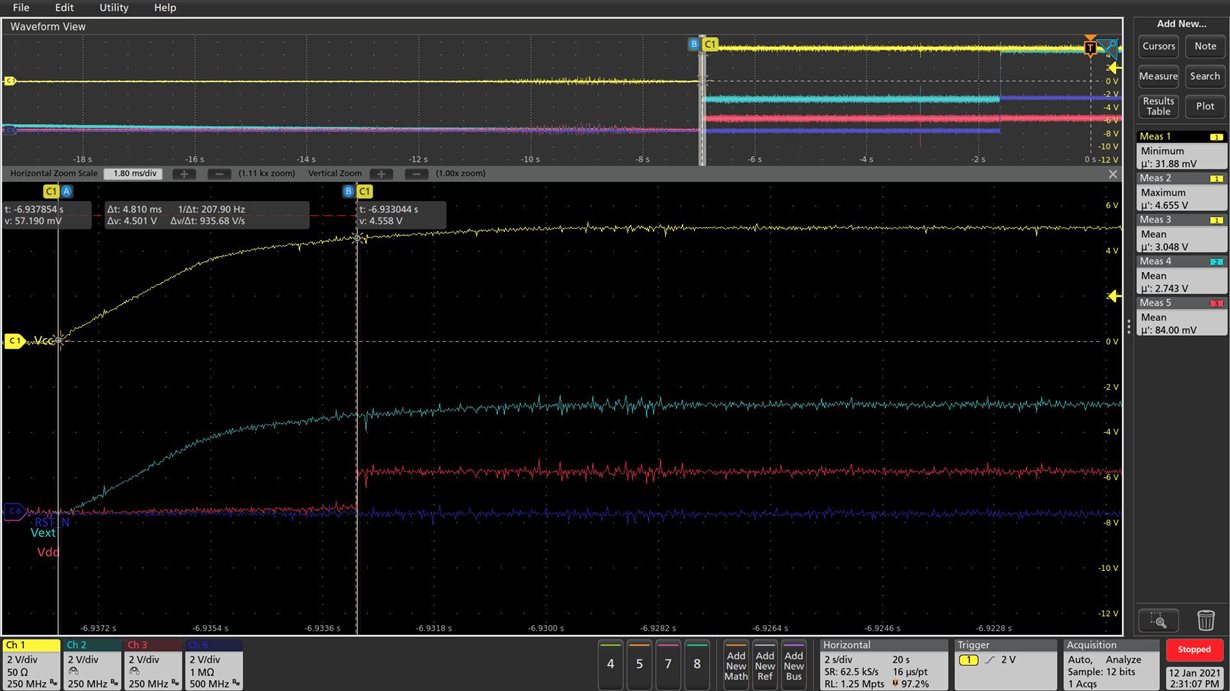

Below is a scope trace showing Vdd when PGA411-Q1 is stuck in reset, Vdd turns on in 3.2ms with RESET_N being low.

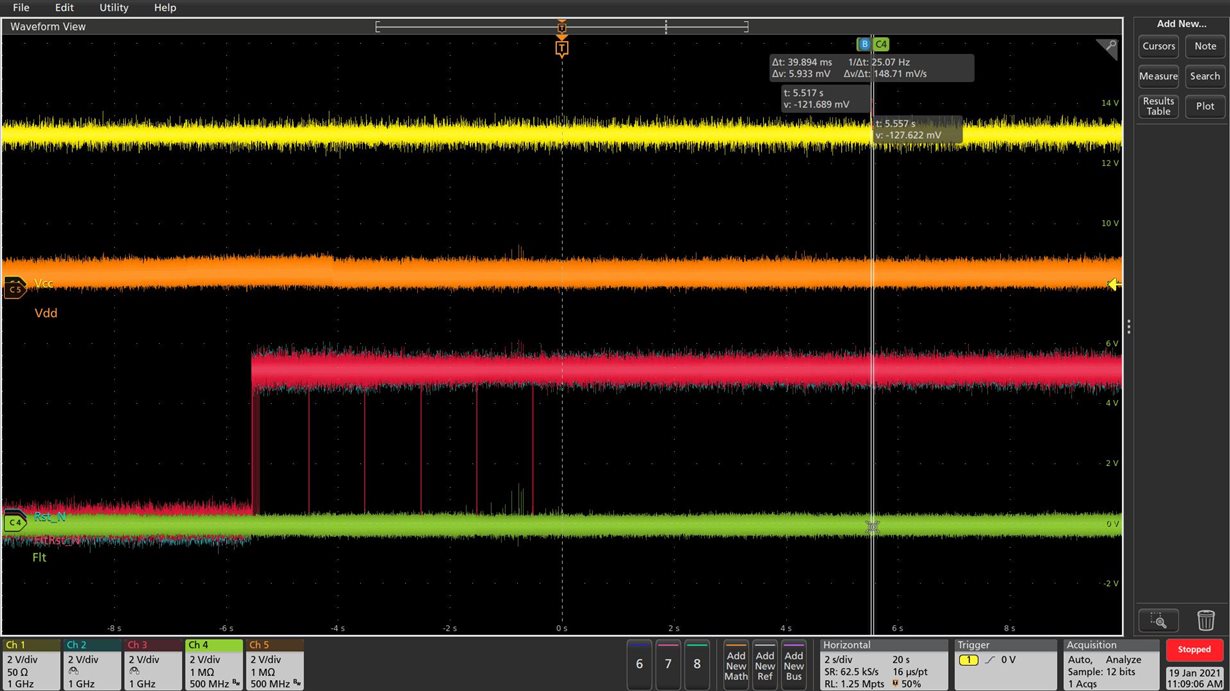

Below is a scope trace showing Vdd when PGA411-Q1 works and Vdd turning to 1.8V in 4.8ms with RESET_N being low. When RESET_N is high, Vext boost regulator turns on showing the PGA411-Q1 has entered the diagnostic state. Another note, our Vcc rail takes 7ms to reach 5V instead of the defined 4ms in the documentation. But still, I don't understand why Vdd is turning on in the RESET state?