Hello team,

I have two questions about SPI of AWR2243:

1. the max speed of SPI supported is 40MHz, 2 SPI clocks means 50ns delay, but if SPI runs 1MHz, 2 SPI clocks means 2us. Page 21 of mmWave-Radar-Interface-Control.pdf instructions isn clear because SPI run different speed, 2 SPI clocks means different time, delay 1us is enough for SPI delay between CS going low and start of SPI clk is enough?

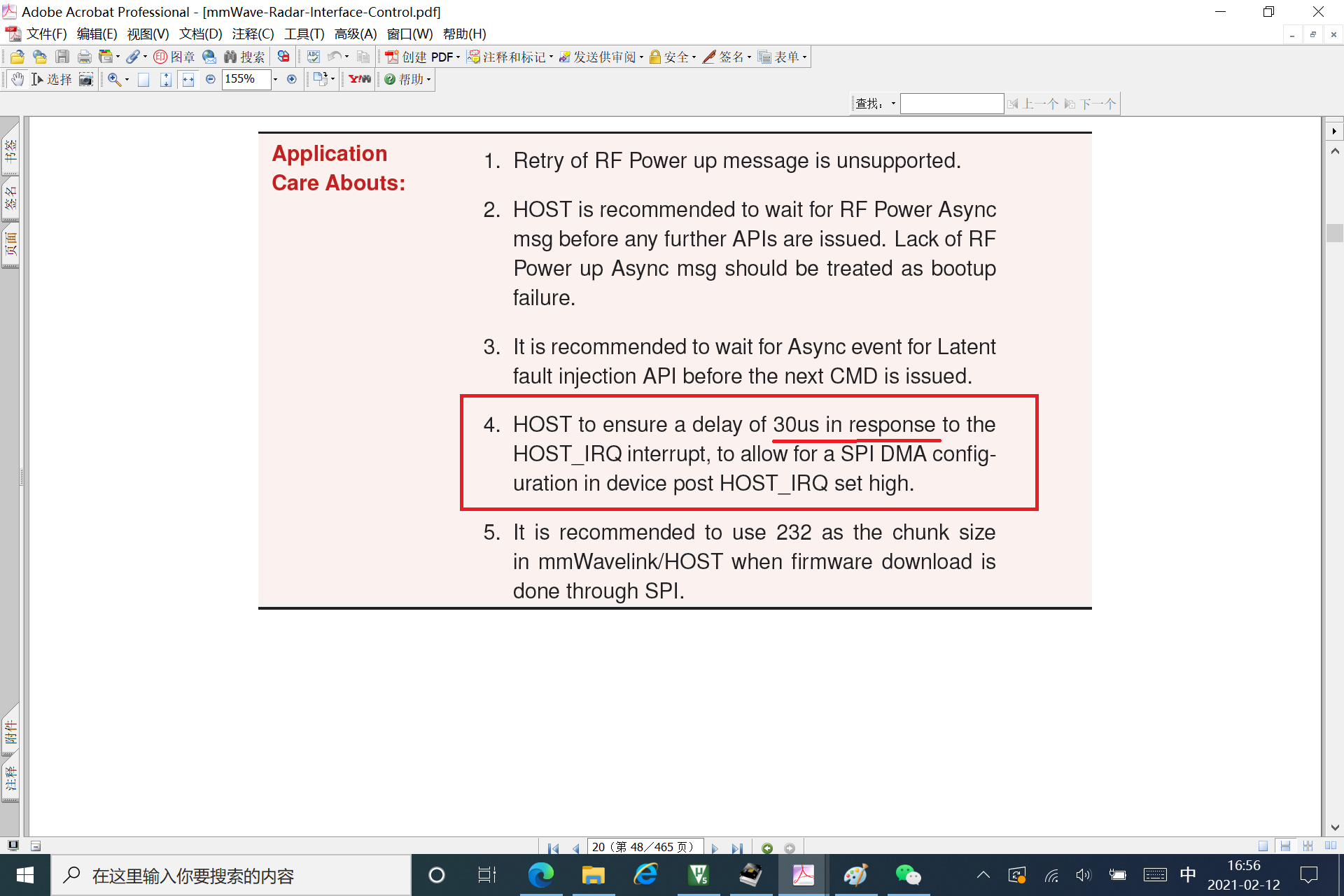

2. HOST ensure a delay of 30us in response to HOST_IRQ interrupt.-----this means when HOST receive IRQ, HOST should delay 30us, then reset CS to low, then start SPI clk, is it right?

thanks for your advice.