Hello,

I am working for develop a system of measuring capacitance by FDC1004. The system is contain a FDC and a microcontroller thru I2C simply. My question is a consistency of CAPDAC.

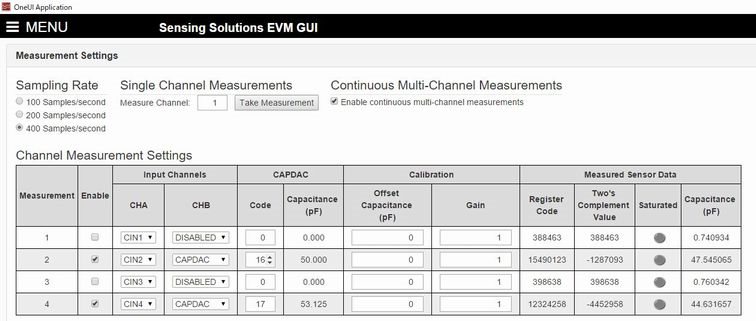

In this case, the measurement target is having the fixed capacitance near around 50pF like this.

(Diff is the difference from CAPDAC zero. acquiring software is my own making.)

(Diff is the difference from CAPDAC zero. acquiring software is my own making.)

But that capacitance is suddenly moving when I change the CAPDAC.

No such the phenomenon is occurring at the other range of CAPDAC and the capacitance of measurement target. This is near around 50pF.

I read some of other posts but this case is not only restricted the capacitance range but also difference of capacitance is huge. Let me know your opinion.

Other setting of registers are RATE=100S/s, no offset calibration and no gain calibration.

Thanks,

KOH