Hi:

I use AWR1843 Demo project, found that ADC Buf configured like this:

dataFormat.adcOutFormat = 0;

dataFormat.channelInterleave = 1;/* Sample Interleave must be I(MSB) Q(LSB) for HWA usage. */

dataFormat.sampleInterleave = 1;

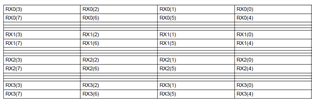

But I found that AWR1843 is litter endian, channelInterleave = 1 means that ADC data stroed in memory frome low should like:

in each data Q(imag part) data should be at low address, and I(real part) should be at high address, like:

Rx0(3)_Q/Rx0(3)_I Rx0(2)_Q/Rx0(2)_I Rx0(1)_Q/Rx(1)_I Rx0(0)_Q/Rx0(0)_I

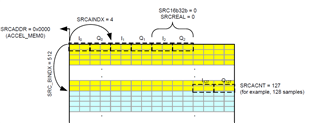

But HWA needs I(real part) at low address, and Q(imag part) at high address,

the configure seems not match HWA input.