Other Parts Discussed in Thread: DCA1000EVM, AWR1642, AWR1243

Hello experts, i'm Kim.

I have 2 questions about DCA1000 and AWR2243 raw data.

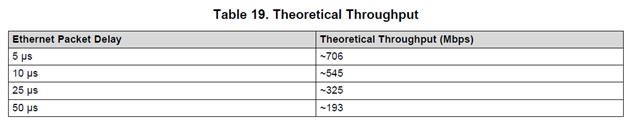

1. Based on the DCA1000 datasheet, the throughput can be changed with different ethernet packet delay.

However, it seems that the maximum value is ~706Mbps with 5us delay time.

Can you explain the meaning of packet delay time in this case, and plus, can we reduce the packet delay to increas the maximum throughput?

(i think the DCA1000 board uses 1000base-T ethernet phy chip, so the potential would be 1Gbps. is the reason of that comparably lower throughput caused by FPGA?)

2. When we use sub-frame mode, can we send just some portion of the sub-frame?

For example, if we use 'a' and 'b' sub frame mode (ab, ab, ab, ab....etc.), can we only get 'b' part ADC data through the DCA1000?

(the reason why i ask this question is to reduce the total raw data size to fit the limited throughput)