Hi,

I tried to run Test_XWR1xxxWithXWR1xxx with two xWR1843BOOSTs. I tried default lib and the lib I rebuild with multi icount enabled (#define SPI_MULT_ICOUNT_SUPPORT).

But I met error when the bitrate is bigger than 20Mhz. Pls find error log below.

default spi lib:

[Cortex_R4_0] ****************************************** Debug: MibSPI Driver Test Application Start ****************************************** Feature: SPI_open API test (instance=0): Passed Debug: SPI Instance @0800fe6c has been opened successfully Debug: SPI Instance @0800fe6c has been closed successfully Debug: Passed DMA channel number check Feature: SPI_open API test - DMA channel validation (instance=0): Passed Feature: SPI_open API test - chip select validation (instance=0): Passed Feature: SPI_open API test - data size validation (instance=0): Passed Feature: SPI_open API test - bit rate validation (instance=0): Passed Debug: Open the SPI Instance for SPI transfer parameter check test Debug: SPI_transfer with data size = 1 failed with error=6. Feature: SPI_transfer API test - data size=1 validation (instance=0): Passed Debug: SPI_transfer with data size = 11 failed with error=6. Feature: SPI_transfer API test - data size=11 validation (instance=0): Passed Debug: SPI_transfer failed with NULL pointers for both TX and RX. Feature: SPI_transfer API test - buffer address validation (instance=0): Passed Debug: SPI Instance @0800fe6c has been closed successfully Debug: Finished API Test for SPIA! Feature: SPI_open API test (instance=1): Passed Debug: SPI Instance @0800fe78 has been opened successfully Debug: SPI Instance @0800fe78 has been closed successfully Debug: Passed DMA channel number check Feature: SPI_open API test - DMA channel validation (instance=1): Passed Feature: SPI_open API test - chip select validation (instance=1): Passed Feature: SPI_open API test - data size validation (instance=1): Passed Feature: SPI_open API test - bit rate validation (instance=1): Passed Debug: Open the SPI Instance for SPI transfer parameter check test Debug: SPI_transfer with data size = 1 failed with error=6. Feature: SPI_transfer API test - data size=1 validation (instance=1): Passed Debug: SPI_transfer with data size = 11 failed with error=6. Feature: SPI_transfer API test - data size=11 validation (instance=1): Passed Debug: SPI_transfer failed with NULL pointers for both TX and RX. Feature: SPI_transfer API test - buffer address validation (instance=1): Passed Debug: SPI Instance @0800fe78 has been closed successfully Debug: Finished API Test for SPIB! Debug: SPI Instance(0) @0800fe6c has been opened successfully Debug: SPI Instance(1) @0800fe78 has been opened successfully Feature: SPI_open API test for two instances: Passed Debug: SPI Instance(0) @0800fe6c has been closed successfully Debug: SPI Instance(1) @0800fe78 has been closed successfully Debug: SPI Instance(0) @0800fe6c has been opened successfully Debug: passed DMA channel number check for two SPI instances. Feature: SPI_open API test for two instances: DMA channel validation: Passed Debug: SPI Instance @0800fe6c has been closed successfully Debug: Finished API Test for SPIA + SPIB! Debug: SPI Instance @0800fe6c has been reopened in MASTER mode successfully Master: Start SPI Write test with XWR1xxx Master write Throughput = 0.9363 Mbps Master: Start SPI Read test with XWR1xxx Debug: Master read Throughput = 0.9363 Mbps Master: Start SPI Data echo test with XWR1xxx Master: recv msg: magic=3456, dataLen=16, seq=1 Master: Synced with Slave, start data echo test Feature: SPI 4Pin mode Master test at bitRate 1000 Kbps : Passed Debug: 4pin mode 1MHz passed! Debug: SPI Instance @0800fe6c has been reopened in MASTER mode successfully Master: Start SPI Write test with XWR1xxx Master write Throughput = 1.7589 Mbps Master: Start SPI Read test with XWR1xxx Debug: Master read Throughput = 1.7589 Mbps Master: Start SPI Data echo test with XWR1xxx Master: recv msg: magic=3456, dataLen=16, seq=1 Master: Synced with Slave, start data echo test Feature: SPI 4Pin mode Master test at bitRate 2000 Kbps : Passed Debug: 4pin mode 2MHz passed! Debug: SPI Instance @0800fe6c has been reopened in MASTER mode successfully Master: Start SPI Write test with XWR1xxx Master write Throughput = 4.2767 Mbps Master: Start SPI Read test with XWR1xxx Debug: Master read Throughput = 4.2767 Mbps Master: Start SPI Data echo test with XWR1xxx Master: recv msg: magic=3456, dataLen=16, seq=1 Master: Synced with Slave, start data echo test Feature: SPI 4Pin mode Master test at bitRate 6000 Kbps : Passed Debug: 4pin mode 6MHz passed! Debug: SPI Instance @0800fe6c has been reopened in MASTER mode successfully Master: Start SPI Write test with XWR1xxx Master write Throughput = 5.9228 Mbps Master: Start SPI Read test with XWR1xxx Debug: Master read Throughput = 5.9234 Mbps Master: Start SPI Data echo test with XWR1xxx Master: recv msg: magic=3456, dataLen=16, seq=1 Master: Synced with Slave, start data echo test Feature: SPI 4Pin mode Master test at bitRate 10000 Kbps : Passed Debug: 4pin mode 10MHz passed! Debug: SPI Instance @0800fe6c has been reopened in MASTER mode successfully Master: Start SPI Write test with XWR1xxx Master write Throughput = 8.4140 Mbps Master: Start SPI Read test with XWR1xxx Debug: Master read Throughput = 8.4120 Mbps Master: Start SPI Data echo test with XWR1xxx Master: recv msg: magic=3456, dataLen=16, seq=1 Master: Synced with Slave, start data echo test Feature: SPI 4Pin mode Master test at bitRate 20000 Kbps : Passed Debug: 4pin mode 20MHz passed! Debug: SPI Instance @0800fe6c has been reopened in MASTER mode successfully Master: Start SPI Write test with XWR1xxx Master write Throughput = 10.6430 Mbps Master: Start SPI Read test with XWR1xxx Debug: Master read Throughput = 10.6445 Mbps Master: Start SPI Data echo test with XWR1xxx Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0

spi lib with multi icount enabled:

****************************************** Debug: MibSPI Driver Test Application Start ****************************************** Feature: SPI_open API test (instance=0): Passed Debug: SPI Instance @0800fe6c has been opened successfully Debug: SPI Instance @0800fe6c has been closed successfully Debug: Passed DMA channel number check Feature: SPI_open API test - DMA channel validation (instance=0): Passed Feature: SPI_open API test - chip select validation (instance=0): Passed Feature: SPI_open API test - data size validation (instance=0): Passed Feature: SPI_open API test - bit rate validation (instance=0): Passed Debug: Open the SPI Instance for SPI transfer parameter check test Debug: SPI_transfer with data size = 1 failed with error=6. Feature: SPI_transfer API test - data size=1 validation (instance=0): Passed Debug: SPI_transfer with data size = 11 failed with error=6. Feature: SPI_transfer API test - data size=11 validation (instance=0): Passed Debug: SPI_transfer failed with NULL pointers for both TX and RX. Feature: SPI_transfer API test - buffer address validation (instance=0): Passed Debug: SPI Instance @0800fe6c has been closed successfully Debug: Finished API Test for SPIA! Feature: SPI_open API test (instance=1): Passed Debug: SPI Instance @0800fe78 has been opened successfully Debug: SPI Instance @0800fe78 has been closed successfully Debug: Passed DMA channel number check Feature: SPI_open API test - DMA channel validation (instance=1): Passed Feature: SPI_open API test - chip select validation (instance=1): Passed Feature: SPI_open API test - data size validation (instance=1): Passed Feature: SPI_open API test - bit rate validation (instance=1): Passed Debug: Open the SPI Instance for SPI transfer parameter check test Debug: SPI_transfer with data size = 1 failed with error=6. Feature: SPI_transfer API test - data size=1 validation (instance=1): Passed Debug: SPI_transfer with data size = 11 failed with error=6. Feature: SPI_transfer API test - data size=11 validation (instance=1): Passed Debug: SPI_transfer failed with NULL pointers for both TX and RX. Feature: SPI_transfer API test - buffer address validation (instance=1): Passed Debug: SPI Instance @0800fe78 has been closed successfully Debug: Finished API Test for SPIB! Debug: SPI Instance(0) @0800fe6c has been opened successfully Debug: SPI Instance(1) @0800fe78 has been opened successfully Feature: SPI_open API test for two instances: Passed Debug: SPI Instance(0) @0800fe6c has been closed successfully Debug: SPI Instance(1) @0800fe78 has been closed successfully Debug: SPI Instance(0) @0800fe6c has been opened successfully Debug: passed DMA channel number check for two SPI instances. Feature: SPI_open API test for two instances: DMA channel validation: Passed Debug: SPI Instance @0800fe6c has been closed successfully Debug: Finished API Test for SPIA + SPIB! Debug: SPI Instance @0800fe6c has been reopened in MASTER mode successfully Master: Start SPI Write test with XWR1xxx Master write Throughput = 0.9363 Mbps Master: Start SPI Read test with XWR1xxx Debug: Master read Throughput = 0.9363 Mbps Master: Start SPI Data echo test with XWR1xxx Master: recv msg: magic=3456, dataLen=16, seq=1 Master: Synced with Slave, start data echo test Feature: SPI 4Pin mode Master test at bitRate 1000 Kbps : Passed Debug: 4pin mode 1MHz passed! Debug: SPI Instance @0800fe6c has been reopened in MASTER mode successfully Master: Start SPI Write test with XWR1xxx Master write Throughput = 1.7589 Mbps Master: Start SPI Read test with XWR1xxx Debug: Master read Throughput = 1.7588 Mbps Master: Start SPI Data echo test with XWR1xxx Master: recv msg: magic=3456, dataLen=16, seq=1 Master: Synced with Slave, start data echo test Feature: SPI 4Pin mode Master test at bitRate 2000 Kbps : Passed Debug: 4pin mode 2MHz passed! Debug: SPI Instance @0800fe6c has been reopened in MASTER mode successfully Master: Start SPI Write test with XWR1xxx Master write Throughput = 4.2759 Mbps Master: Start SPI Read test with XWR1xxx Debug: Master read Throughput = 4.2766 Mbps Master: Start SPI Data echo test with XWR1xxx Master: recv msg: magic=3456, dataLen=16, seq=1 Master: Synced with Slave, start data echo test Feature: SPI 4Pin mode Master test at bitRate 6000 Kbps : Passed Debug: 4pin mode 6MHz passed! Debug: SPI Instance @0800fe6c has been reopened in MASTER mode successfully Master: Start SPI Write test with XWR1xxx Master write Throughput = 5.9259 Mbps Master: Start SPI Read test with XWR1xxx Debug: Master read Throughput = 5.9240 Mbps Master: Start SPI Data echo test with XWR1xxx Master: recv msg: magic=3456, dataLen=16, seq=1 Master: Synced with Slave, start data echo test Feature: SPI 4Pin mode Master test at bitRate 10000 Kbps : Passed Debug: 4pin mode 10MHz passed! Debug: SPI Instance @0800fe6c has been reopened in MASTER mode successfully Master: Start SPI Write test with XWR1xxx Master write Throughput = 8.4142 Mbps Master: Start SPI Read test with XWR1xxx Debug: Master read Throughput = 8.4043 Mbps Master: Start SPI Data echo test with XWR1xxx Master: recv msg: magic=3456, dataLen=16, seq=1 Master: Synced with Slave, start data echo test Feature: SPI 4Pin mode Master test at bitRate 20000 Kbps : Passed Debug: 4pin mode 20MHz passed! Debug: SPI Instance @0800fe6c has been reopened in MASTER mode successfully Master: Start SPI Write test with XWR1xxx Master write Throughput = 10.6480 Mbps Master: Start SPI Read test with XWR1xxx Debug: Master read Throughput = 10.6442 Mbps Master: Start SPI Data echo test with XWR1xxx Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0 Master: recv msg: magic=9a2b, dataLen=32776, seq=0

I have two questions. Would you pls help?

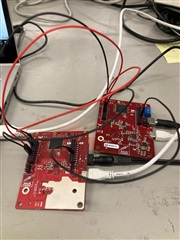

1. The issue happens with higher clock. Is it due the line I connected two boards are too long? Pls find my setup below.

2. Why the throughput with and without multi icount enable is similar? I suppose when multi icount enabled, the throughput should be higher?