Other Parts Discussed in Thread: AWR1443, , AWR1642

Hi,

In AWR1243 datasheet, I can't find detail info of pin definition for LVDS. In AWR1443 EVM schematic, I found HS_DEBUG1 is for LVDS_FRCLK and HS_DEBUG2 is for LVDS_VALID.

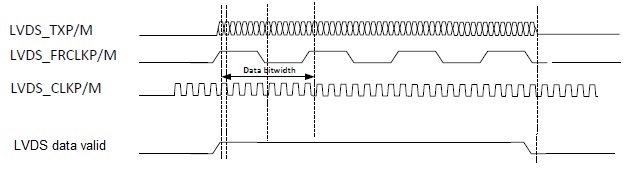

I found a LVDS timing in Figure 13-5. LVDS Interface Timings of swru520.pdf (awr14_16_trm), but there is no info about LVDS valid signal. Would you pls kindly advise the timing of LVDS Valid?