Tool/software:

Hi,

<Question>

Could you tell me why the voltage of VREG becomes 4V?

Could you tell me why the voltage of VREG changes to 5V after a certain time, and why the voltage drop of VOUT occurs?

<Background>

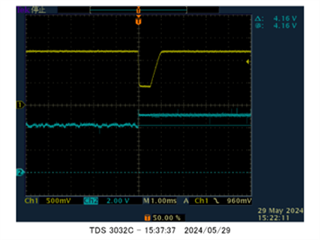

For several hours after the power is turned on, the voltage of VREG becomes 4V.

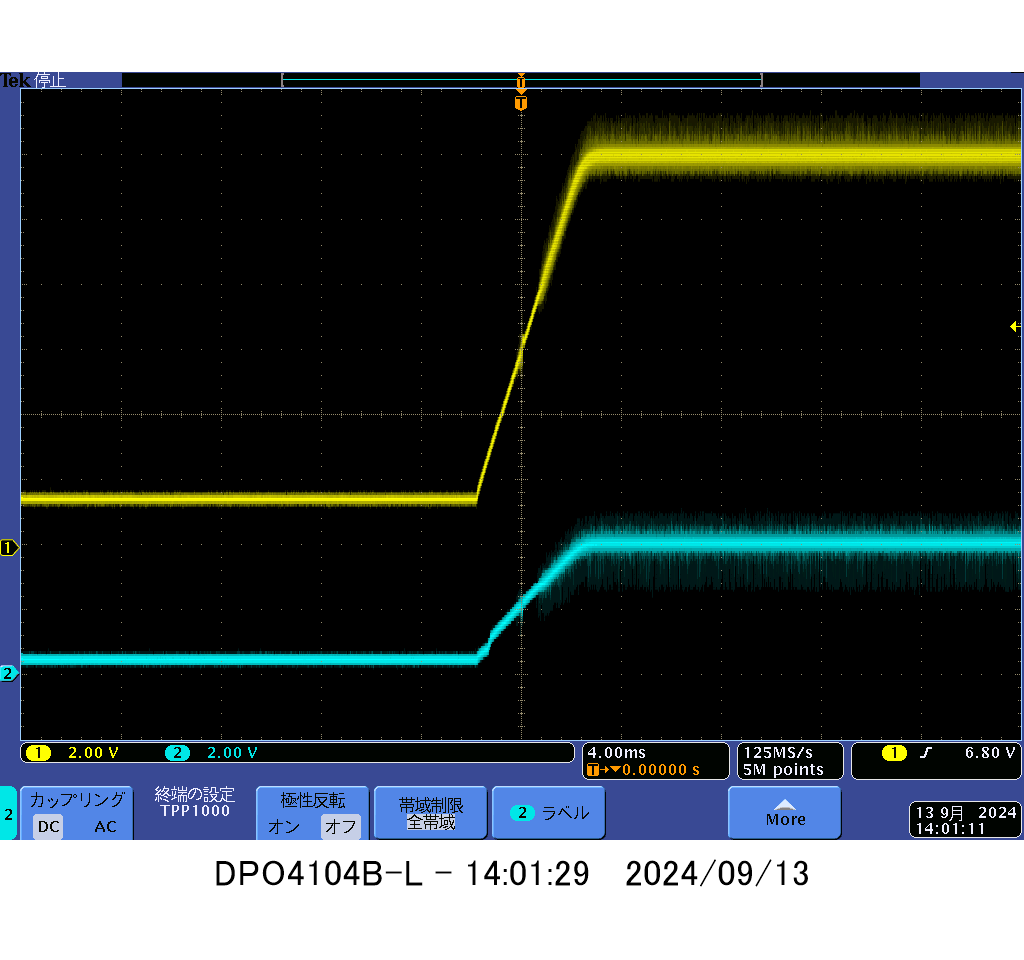

After a few hours, VREG (2ch) changes to 5V and the voltage of VOUT (1ch) drops as shown in the attached waveform.

At this time, the device is not operated (there is almost no load fluctuation).

Best Regards,

Nishie