Hi Team,

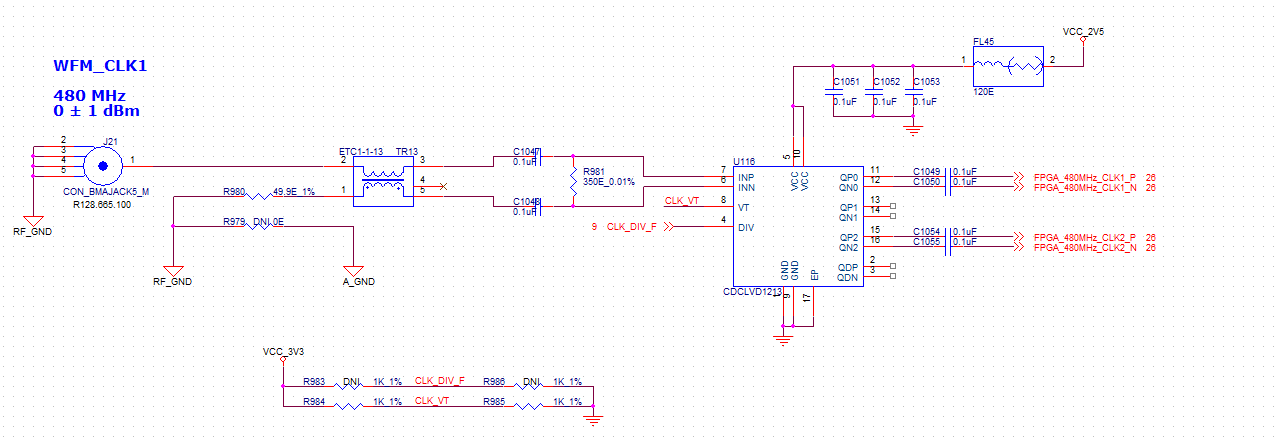

I am receiving a 480 MHz, 0 dBm signal from an external board, which needs to be split and fed to both the DAC and FPGA on my board.

As per the CDCLVD1213 datasheet, the supported input amplitude range is 0.3 Vpp to 1.6 Vpp. I would like to confirm whether my attached schematic meets this requirement.

If not, please suggest an alternative part that can support this specification.

Kindly do the needful.