Other Parts Discussed in Thread: , TXB0304, TXU0104

Hi

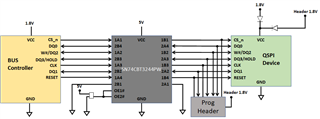

We are using a circuit like shown in the below image.

A programming header is provided for programming the device for the first time. A header logic is implemented for OE# to disable the IC, provides isolation between Bus controller and QSPI device during the programming. The 1.8V supply for both controller and QSPI device is isolated so that power from the header will not leak to controller power at this stage.

As per the datasheet the the SN74CBT3244 supports " Data I/Os Support 0- to 5-V Signaling Levels (0.8V, 1.2 V, 1.5 V, 1.8 V, 2.5 V, 3.3 V, 5 V).

But on the table "6.3 Recommended Operating Conditions" it is suggested the VIH as 2.0V and VIL as 0.8V

If the VIH and VIL levels specified are applicable to the Input and output pins how it can support 1.8V?

QSPI maximum operating speed 62.5MHz in the fast read mode.

Query

1. Is the circuit will work? That is can we use the SN74CBT3244 as a 1.8V QSPI buffer?

2. If the VIH and VIL levels specified are applicable to the Input and output pins how it can support 1.8V?

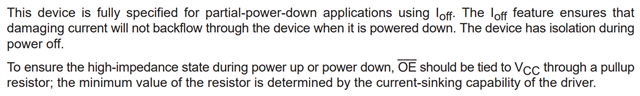

3. In sequence if 5V is coming up first and then 1.8V for Bus controller and QSPI device, is this going to damage any of the Bus controller or QSPI device in a common scenario?

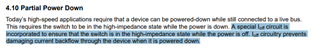

4. Is the SN74CBT3244 will damage if we connect the programmer of 1.8V for programming the QSPI device and SN74CBT3244 is not powered.(5V applied)

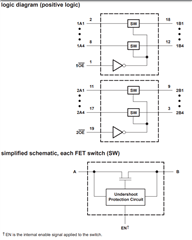

5. Is it ok connecting the controller signals everything on the left and device signals everything on the right side? (I can see A and B sides are shuffled in the IC). The current connection shall help in easy routing

6. If the buffer is not ok for the above purpose please help me to find a suitable buffer IC.

.