Mobile Industry Processor Interface (MIPI) is a protocol primarily used for high speed interfacing by smart phones, cameras, tablets, displays, and many other devices. A MIPI system consists of data line groups called lanes which work together to create a link whose total bandwidth defines the resolution and bit rate of the system. The advantage of this is many lanes can be used in parallel to increase the link bandwidth while keeping the per lane bandwidth much lower. When looking for an MIPI analog switch / multiplexer it’s important to understand the specifications of the various MIPI configurations.

- Differential signaling

- Voltage levels: 1.2V, 2.5V, 3.3V

- Frequency: Up to 2.5GHz per lane, typically ~1GHz per lane

Common Configurations:

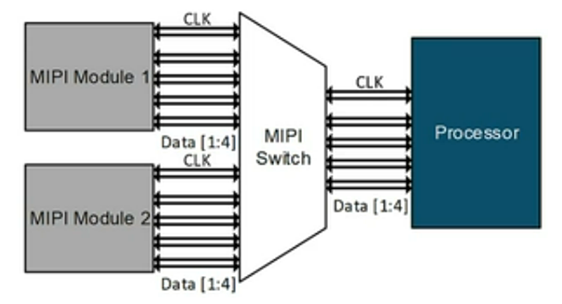

D-PHY

This configuration consists of up to 4 data differential pairs plus a clock differential pair. All of the lanes operate together and are both sampled on the rising and falling edge of the clock. Compared to the newer C-PHY configuration, D-PHY does require more signal lines but it has reduced signal processing complexity.

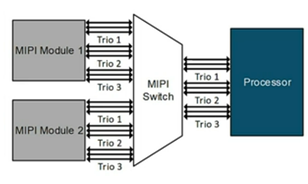

C-PHY

This configuration contains trios of data lines without the need for a dedicated clock pair. Each line in the trio is compared to create differential signals. Because of the enhanced encoding, the per lane bit rate can be up to 40% slower, while using less signals, to achieve the same per link bit rate as D-PHY. The trade off is more complicated signal processing for the encoding/decoding.

Both configurations can scale up or down the number of lanes depending on the system need. The minimum requirement is only 1 data lane, which is very beneficial for lower resolution and low power applications.

The below table is a recommendation for multiplexers that can pass MIPI signals on the data signal paths. These devices are controlled via GPIO.

|

MIPI Switch/Multiplexer Selection Guide |

||||

| Device |

Configuration |

Channels | Per Channel Bandwidth (-3 dB) |

Package (Dimensions) |

| TMUX1575 |

2:1 SPDT |

4 | 1.8 GHz | WCSP (1.33mm x 1.33mm) |

| TMUX646 | 2:1 SPDT | 10 | 6.0 GHz | nFBGA (2.45mm x 2.45mm) |

| TS3DDR4000 | 2:1 SPDT | 12 | 6.0 GHz | DSBGA (3mm x 8mm) |

| TS3DV642-Q1 | 2:1 SPDT | 12 | 5.8 GHz | WQFN (3.5mm x 9mm) |

For more information on MIPI and our portfolio, please refer to our TI Precision Labs video and product overview