Other Parts Discussed in Thread: TS3L501E

Hi,

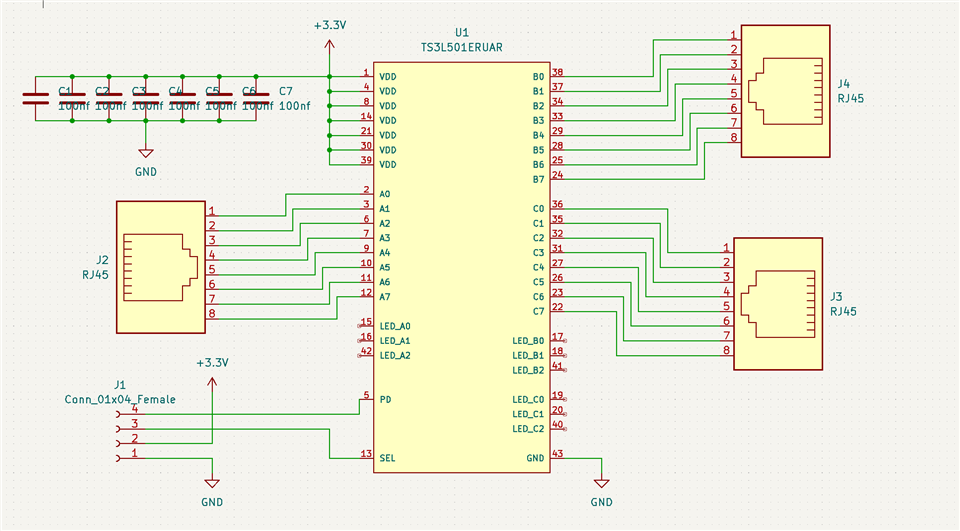

I want to create a module based on TS3A27518ERTWR to switch b/w two networks. Network may be 10Mbps, 100Mbps or 1000Mbps. The idea is to connect three RJ-45 connectors to multiplexed pins as shown below:

I have the following questions:

- Can it be used to route 10Mbps, 100Mbps or 1000Mbps signals from Ax pins to two different targets (connected to Bx, Cx pins)?

- Any obvious problems with above schematic?

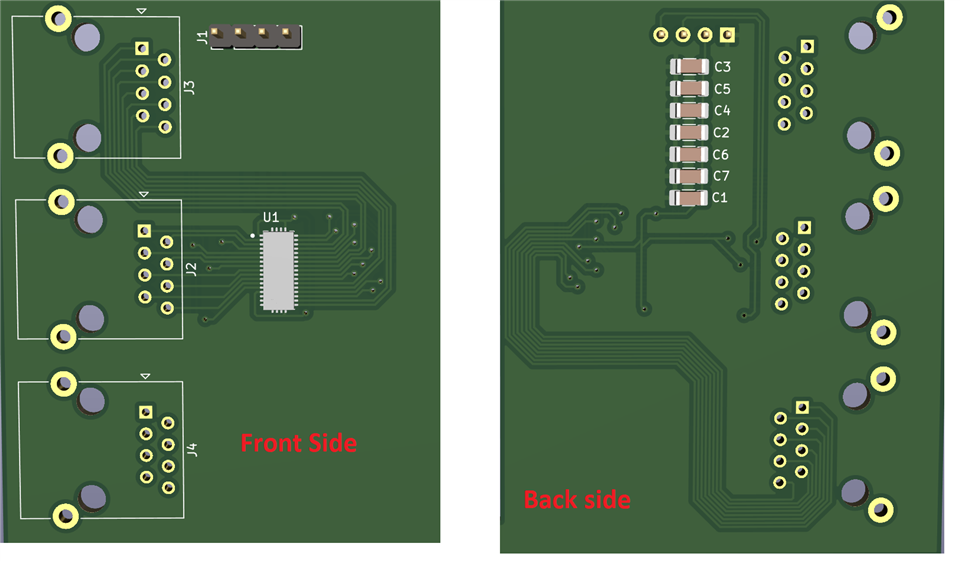

- The traces are routed as below, is there a problem with these routing. I mean in the Network cable, there are 4 pairs of two two wires (total 8 wires) but on PCB should these pair wires be kept close to each other or plan 8-wires are fine as shown below.

- There are few vias, that I cannot avoid, will they be problematic?

- The traces width is 0.25mm which should be increased a bit?

Thanks in advance.

Waiting for the recommendations.