Other Parts Discussed in Thread: TMUX7436F

Hi team,

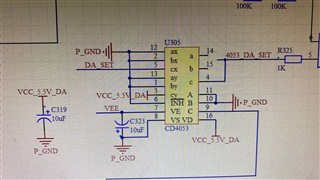

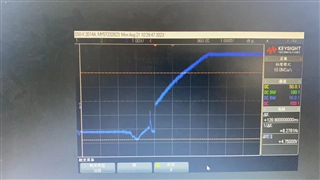

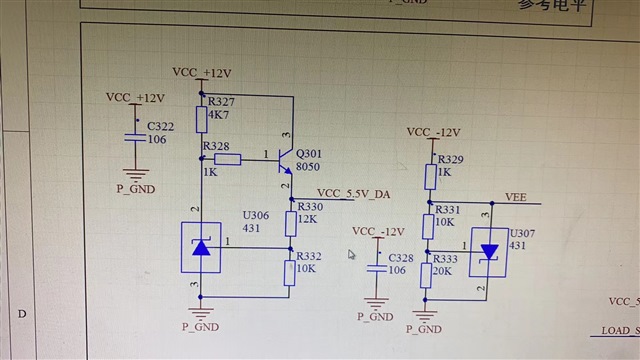

When use the CD4053 for signal selection, but at power up instant, the output signal waveform is undershooed for a while. 5.5VDA is selected by default at power-on. Below are the Sch and signal waveform. What's the reason for that ?Thanks for your response.