What is Latch up?

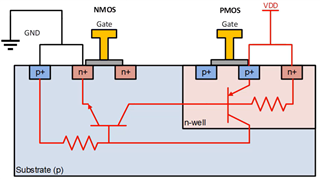

Latch-Up is a condition where a low impedance path is created between a supply pin and ground. This condition is caused by a trigger (current injection or overvoltage), but once activated, the low impedance path remains even after the trigger is no longer present. This low impedance path may cause system unexpected behavior or catastrophic damage due to excessive current levels. The Latch-Up condition typically requires a power cycle to eliminate the low-impedance path.

Figure 1-Typical Latch up in CMOS Device

Using Latch up Immune Multiplexers to Improve System Reliability

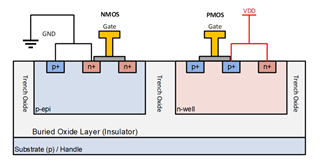

The TMUX72xx,TMUX73xxF,TMUX74xxF,TMUX81xx, and TMUX82xx device families are constructed on a Silicon on Insulator (SOI) based process where an oxide layer is added between the PMOS and NMOS transistor of each CMOS switch to prevent parasitic structures from forming. The latch-up immunity feature allows switches and multiplexers to be used in harsh environments.

Figure 2- Latch up immune CMOS Switch Structure

For more information on latch-up immunity refer to Using Latch Up Immune Multiplexers to Help Improve System Reliability and What is latch-up immunity?