Hello,

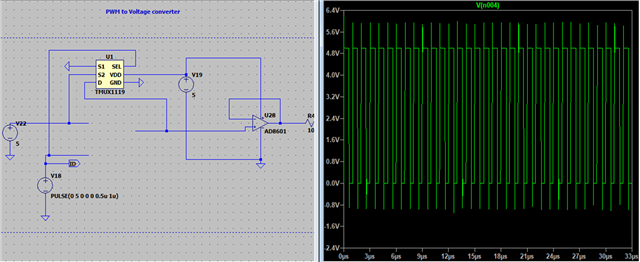

I have attached a SPICE simulation where i found high ripple during switching. Please help me with this.

Regards,

Krunal

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

I have attached a SPICE simulation where i found high ripple during switching. Please help me with this.

Regards,

Krunal

Hello Krunal,

Is the ripple on VDD?

What is the frequency of the signal?

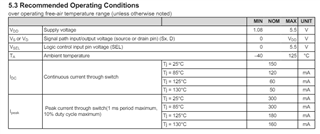

If the ripple is on VDD it seems the signal is exceeding its recommended operational conditions.

Please answer questions above for clarification.

Thanks,

Nir

Hello Nir,

The ripple is observed at D and the frequency is 1 MHz. As per datasheet, Max voltage limit of VDD is 5.5 V and for D is till VDD.

So, i think exceeding the recommendation limit is not case.

Thanks,

Krunal

Hello Krunal,

This seems to be a model level issue. I can recommend adding decoupling capacitors and trying different values. You can start with 100nF caps and see how the signal behaves.

Thanks,

Nir

Hello Nir,

Thanks for recommendation. By adding decoupling capacitor of 24.7nF, output is coming from "D" pin looks better than before and ripple becomes less.

Thanks,

Krunal