Tool/software:

Hi,

I would like to consult about an issue with TI's Switch TMUX154E. There are two problems:

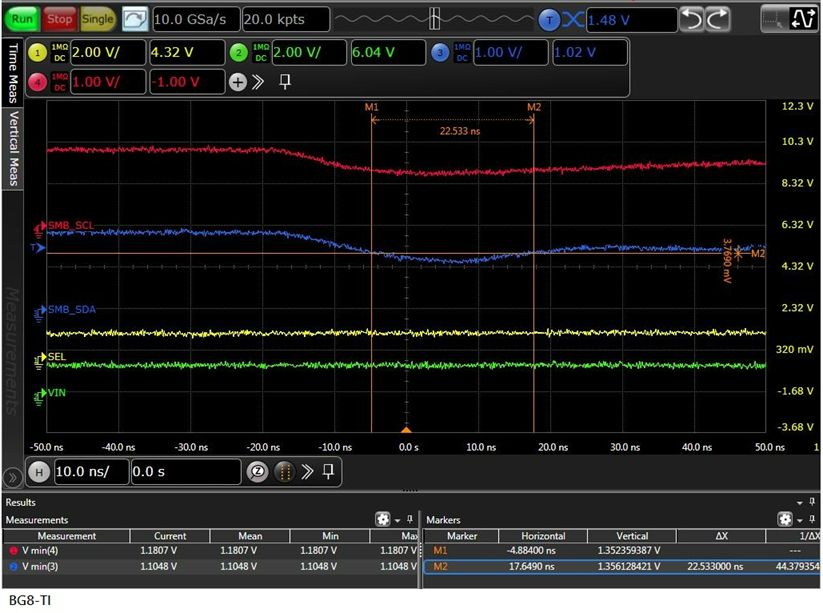

- During power-on, when the switch toggles, a very short drop of approximately 20ns is observed on Port A/B.

- During power-on/off, when the switch toggles, a longer and less severe drop is observed on Port A/B, which appears to be related to the VDD slew rate.

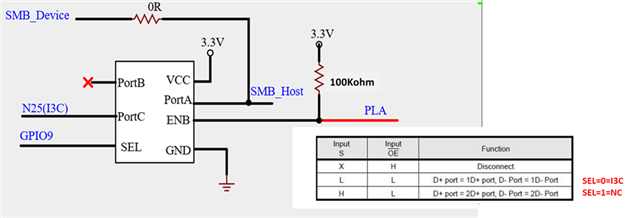

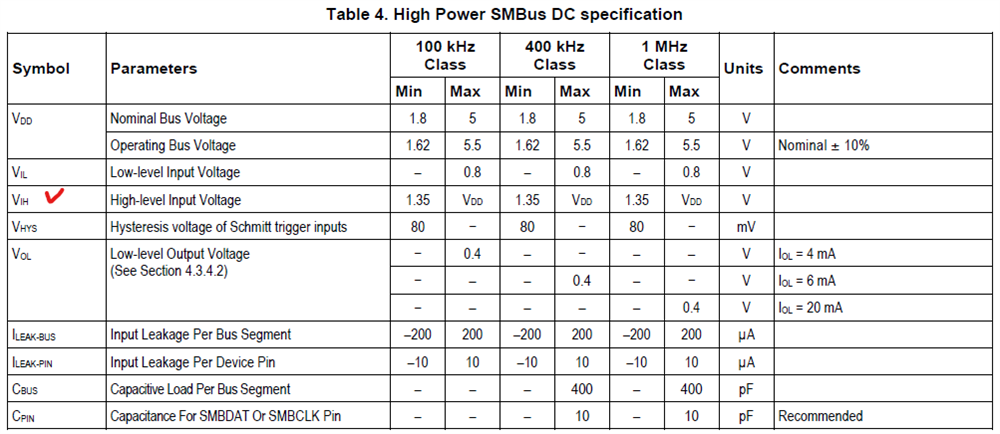

Schematic as below.

The circuit configuration is as follows:

- Port A/B has a constant pull-up OD signal.

- Port A1/B1 is an OD type without pull-up IO.

- Port A0/B0 is a PP type, with an internal pull-up diode to P_1V8 inside our IC.

- Power-on sequence: P_VIN_3V3 rises to 2.7V first, and after 3ms, P_1V8 begins to rise.

- Power-off sequence: P_VIN_3V3 drops to 2.7V, and P_1V8 is turned off.

Question 1: Is the drop caused by the I3C SW being powered, and when SEL switches from 0 to 1, Port A1/B1 is floating, causing Port A/B to charge Port A1/B1, resulting in a brief drop? Or is it due to a momentary effect during the internal switching of the SW that causes this drop?