Tool/software:

Hi,

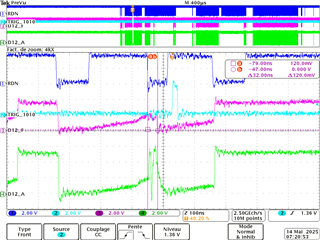

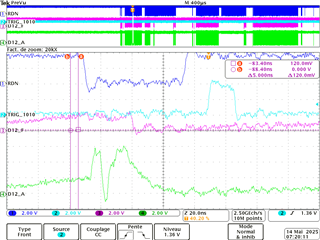

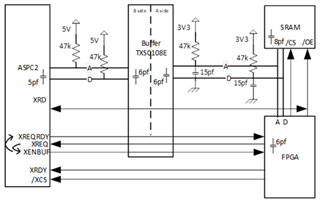

in my design I currently use buffer bi-directional TXS0108E without direction control signal.

On side VCCB I have an ASIC powered in 5V and on the VCCAr side a FPGA + SRAM powered under 3V3.

Each side there are 47k-ohms pull-up resistor.

I would like to know how many time to wait between sending data from A side to B side the B side to A side, I can fing only propagation time in datasheet.

Thanks for your feedbak,

Regards

Denis