Tool/software:

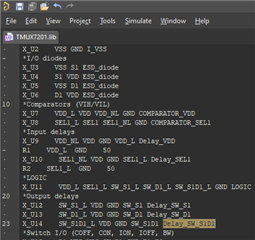

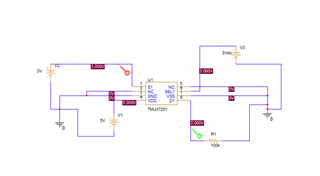

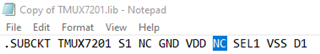

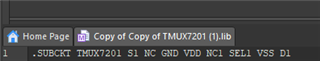

I think the TMUX7201 models are incomplete. When I downloaded the TMUX7201 PSPICE model from TI, I got this error when tried running my simulation:

"The instance `X_U14' is referencing an undefined model or subcircuit, `Delay_SW_S1D1'. Either include the file containing the definition of `Delay_SW_S1D1', or define `Delay_SW_S1D1' before running the simulation."