Tool/software:

Hello TI support,

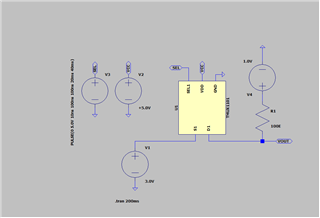

We are trying to use TMUX1101 in gain switching application. However, the PSpice model doesn't seems to provide OFF leakage as per datasheet when tried to test as per datasheet conditions. It gives more leakage even in actual circuit. Could you please check & advise whether,

1. OFF/ ON leakages are modelled in the model.

2. If those are modelled then not sure why it appears 100nA in test circuit? Is there anything being missed from my side?

3. Also how will the OFF leakages change when VSource=0 to 3.3V & Vdrain=3.3 to 0 when supplies are 3.3V. Datasheet conditions are with VS=1V/3V & VD= 3V/1V. Also it will be appreciated if this data is available over -40'C to +85'C.

Regards,

JK