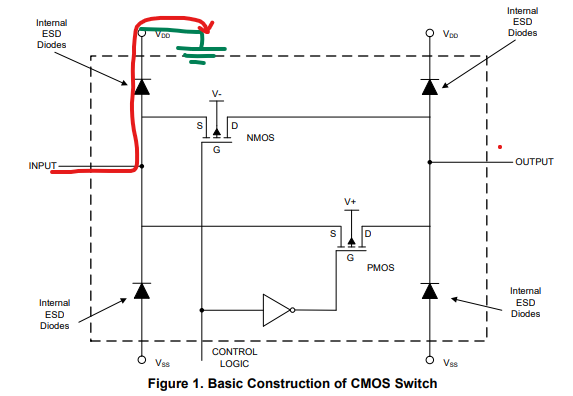

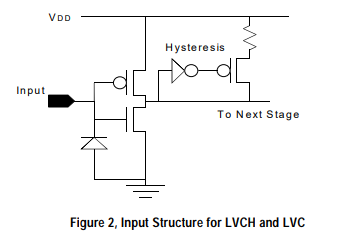

I'm designing a bit of protection for an ADC to deal with inputs which may be powered when the part is not. It appears by the verbiage that the TS5A23166 will get the job done. Yet, as I was going over the data sheet, I became a bit confused by the absolute maximum ratings which state that, for the analog voltages (NO, COM) the maximum is V+ + 0.5V. It amends this by stating that the rating can be exceeded if the clamp current maximums are respected. As described in "Features", the maximum input voltage for the analog signals is not, in fact, limited by the supply voltage (but, likely, some other structure (zener?) which sets the voltage at which the clamp occurs). For example ICs in TIs LVC logic family (which tolerate inputs when VCC is 0V) list their AMR as +6.5V (not related to VCC).

I hope this doesn't come across as picking nits. As I read the spec, the AMR leaves me not knowing at what voltage an input would clamp. Do I have do add current limiting on the driven side of the switch to ensure that the switch (and my analog source) are protected when unpowered?

Because of the holidays, TI E2E™ design support forum responses will be delayed from Dec. 25 through Jan. 2. Thank you for your patience.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.