I have the same issue with Xiaojian, we have 2pcs fail TS3A5018, after TI Failure analysis, it indicates the EIPD on wedge pad, would you please help us to check :

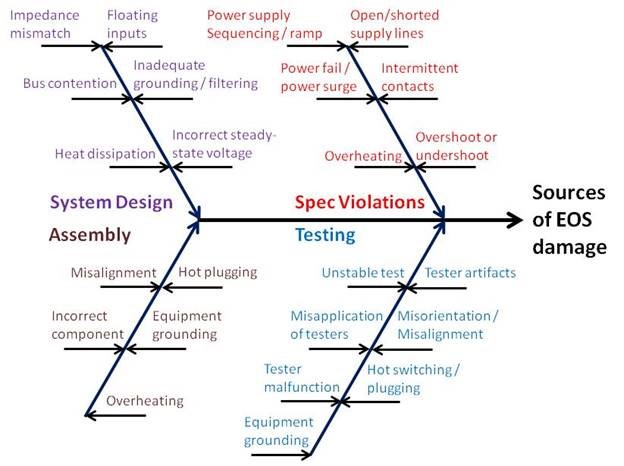

1) which kind of conditions will lead to an EIPD of wedge pad?

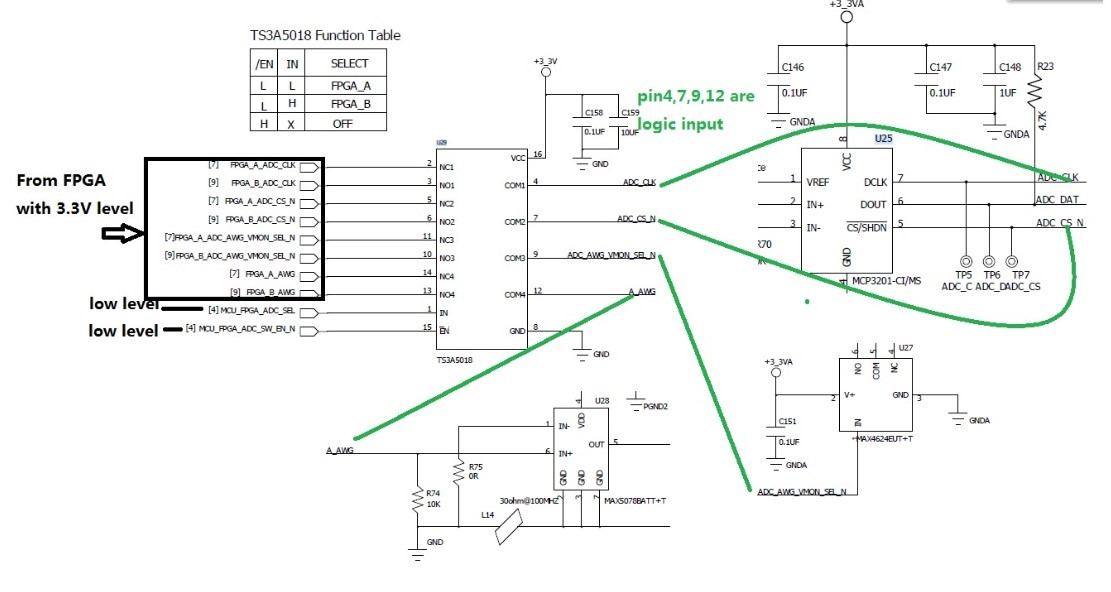

2) can you please help to check whether there is issue with our application?QEM-CCR-2002-00903 FA report.pdf