Other Parts Discussed in Thread: TMUX1511

The question below is a cut / paste from a field person

========

We wanted some clarifications around TMUX1111 with respect to leakage currents under powered off condition.

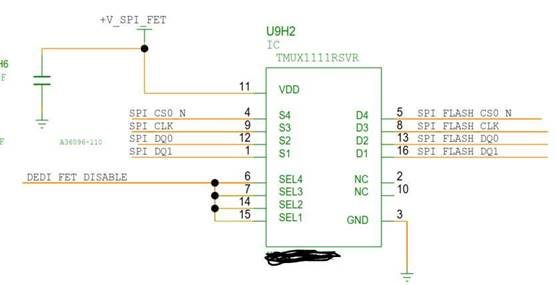

Below is the schematic implementation in our circuit.

Help us with your responses for below

- With VDD supply at off condition and SEL pins at floating, can the above FET SW isolate D from S lines ?

In the above scenario we will have SPI activity at 1.8V level on D lines, which needs to be isolated on S side.

- With VDD supply at off condition and only SEL lines pulled high, will the FET SW isolate D from S lines ?

- Is the above condition recommended for operation ?

- In one of the articles we came across powered-off protection feature on TMUX1511 FET SW. can this provide isolation in the VDD unpowered condition, as per our requirement ?

- Though TMUX1111 datasheet does not specify about powered-off protection, is this feature supported on TMUX1111 as they both are from same family?

- Is there any drop-in replacement chip for TMUX1111 with above feature ?