Other Parts Discussed in Thread: TMUX1237, , SN74LVC1G04

The SN74LVC1G3175 device datasheet lists the break-before-make feature.

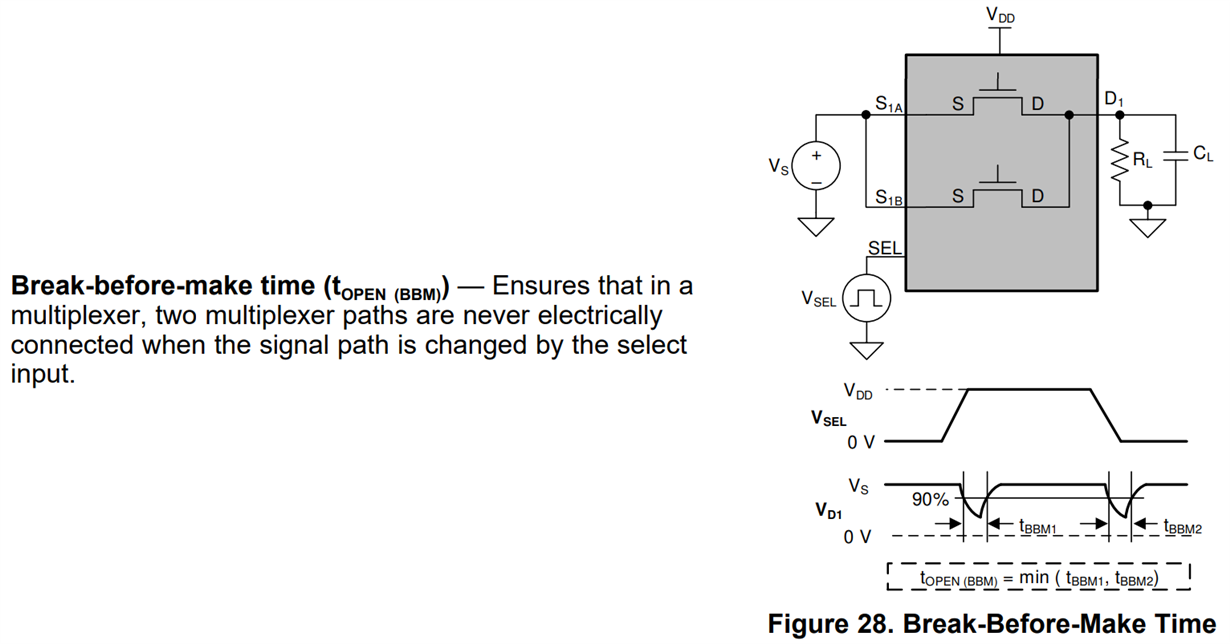

From literature found regarding the BBM feature, it seems power is removed from the output for a short time, when switching between channels, to prevent shorting channels together.

Because of this, the output voltage decays based on the time to discharge the output capacitance.

I am using this literature for reference: SLVAE51–November 2018

My questions is this:

1. With BBM, the output isn't shorted to GND or anything, right? Power is just disconnected, so whatever voltage the output was at, will decay as the charge stored in the output capacitance discharges through various paths to GND.

2. The SN74LVC1G3175 datasheet lists tB-M as MIN 0.5ns. What is this parameter exactly...? Figure 11 from the DS shows a parameter "td"...Is there a maximum switchover time parameter over temperature listed? This is needed to calculate how long the output capacitance will be discharging.

3. If you are switching between two similar voltages (say Ch-1 at 5V to Ch-2 at 5V), and want to minimize the voltage drop at the output, you would increase the output capacitance, right?

4. From the literature SLVAE51, page 10, there are some equations and a graph depicting the expected Vout dip during the switchover process. Is my understanding below accurate?

For SN74LVC1G3175, the switchover time is XXX. I will assume 1ns MAX for now.

We will assume Iout when the output is 5V to be 1mA.

We will assume 30pF of output capacitance.

Then from the equations, Vdip = 1ns * (1mA / 30pF) = 0.03V

Thus, the output voltage will only dip 0.03V. Is this understanding accurate for break-before-make operation w/ such analog switches?

Regards,

Darren