e2e,

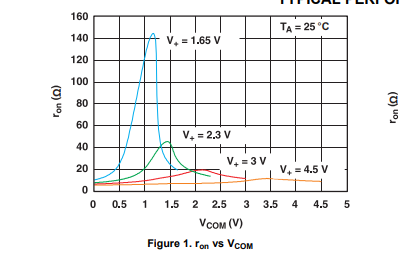

I'm currently using the TS5A33157-Q1 to pass an I2C signal. Due to my system requirements, I would like to operate this mux at 1.8V supply voltage but concerned that the on-state resistance and capacitance at that supply voltage will impact the rising edge of my I2C signal.

I didn't see an IBIS model available for this mux to use in my simulation so I would like your recommendation on how to model this device in my simulation.

Thank you,

Adam

Thank you,

Adam