Hi All,

I would like to ask a group of related questions on debugging.

What is happening when one clicks "debug"? In particular, what is happening when the programs runs to and stops at a breakpoint?

The purpose of breakpoint is to allow the developer to see the status of the "system" when the exection has run to a particular line of code. But how broad is the definition of this "system"?

Take the instance of an EVM board for example: in addition to the DSP CPU itself, there are many other peripherals on the board, including video and audio interface, added memory storage (DDR2 and flash), LED lights, etc. Even within the CPU itself there can still be the difference between the most "central" part such as the arithmetic unit, an extended "core" part such as the megamodule (with cache, DMA, interrupt controller, extended memory controller), and other modules integrated within the chip such as Video Processing Front End in a DaVinci chip.

All components, from the the most central computational part of a CPU, to integrated enhancement modules, to EVM-added components, have their internal registers and sometimes memory storage. After a system has booted and all peripheral modules have been properly initialized, with each cycle of the CPU clock, the whole EVM board works like a huge manufacturing factory comprising numerous workshops operating in synchronization according to their respectively assigned schedule of tasks.

The executable code, stored in the location of .text section as specified in or determined by the linker, is only a very small portion comparing with the grand scale of the manufacturing assembly line. When we have proceeded to particular code line and stopped, what status do we have to enter into the log in order for a useful "debug" to work?

1. Do we have to "freeze" the whole factory? Do we have to stop the operation at units in all levels of the hierarchy, from top management (CPU) to bottomost workshops, and order every one to halt and keep their present gesture? In this way an inspector would be able to examine the details in every single addressable unit, which is of course the best for examination purposes.

2. Do we really shut down all machines? Can we shut down all machines? Can we make a running wheel stop instantly at its current angle? Can we issue the command to units at all levels of the hierarchy, at all distances from the center, at the same time? Imagine the work of the Roman empire: are communication and relay needed for distant provinces? Won't there be delay due to this?

3. And how much is the cost (procedure, time)? Is it affordable to do all these numerous steps just for observing the status of a single variable? How long does it take to restore the previous running state? And after all, considering the lag between different units, is a restoration possible?

I have never considered such questions in my programming experience before. Although DSP development brought all of them to the forefront, they actually also exist in the seemingly simple environment of Windows programming. Perhaps the only situation in which all these consideration do not exist is the pure algorithmic testing case where no I/O or other device coordination needs to be concerned.

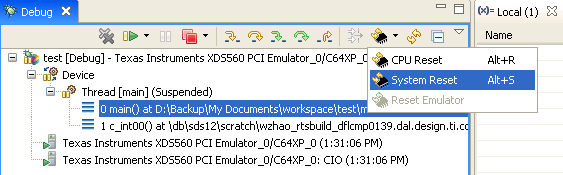

Coming back to a DSP system, what is actually happening when CCS halts at a breakpoint?

1. I think the first principle is a Seperation: all those that can only be changed by the execution of instruction code will remain unchanged due to the halt at the breakpoint. These should include:

1) calling stacks

2) heap, allocation on which is only done by a small group of functions, such as malloc()

3) most of the registers, either within or outside the DSP chip

But there could be complications in this case: For clarity, let's refer to "bits" rather than "registers". Some registers are provided to set the running mode of a device, much the same as buttons on a power plant panel; some are intended to provided as a feedback channel, much the same as a signal light in such a plant. If no instruction code is being executed when CCS halts at a breakpoint, those "buttons" will remain intact, but not necessary the signals.

So if we view a register address containing a "signal" bit, at different times (we first click "view memory" from the menu, key in an address and press "enter", at any possible time, and wait after an arbitrary time, key in the same address or simply refresh this address's value), is it possible for us to see different bit values?

2. 1 considered stacks, heap and registers. What about memory? Even in breakpoint halt I can still see the moving scene captured by the camera is continously being output to the connected display, which is apparently being done by the video processing module within the chip. To achieve this, frames must be written first to a memory address and then being retrieved by the back end video module for output. In this situation, there must at least one block of memory that is being written and read, which are of course coordinated to avoid conflict.

If we attempt to view an address at this block during a breakpoint halt, what will happen? Do we get different values at different times? Are we allowed to read or not?

I am still not able to figure out answers to these questions myself. Could anyone explain them to me?

And in which forum should these questions be asked? Breakpoint is used in CCS, but I also feel that they are intimately related to BIOS and other operating system concepts, and they perhaps also related to the complier, even not that stronger. I know that the policy is to only allow a single post in a single forum, so if this is not the right place, could the moderator help me to move it to the most appropriate forum?

Sincerely,

Zheng