Hello,

I have a dual CPU project for LAUNCHXL-F8379D that runs standalone. I have already flashed the CPUs.

After a fresh launch of UniFlash, verification succeeds on both CPUs but only if I verify in the order CPU1 then CPU2.

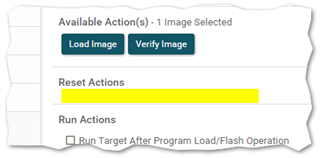

If verification is done in the order CPU2 then CPU1, the latter is not executed. The Verify Program window very, very briefly flashes up but nothing meaningful happens there and there's no console entry. The steps to reproduce are:

Launch UniFlash

Verify CPU1 : OK

Verify CPU2 : OK

Verify CPU1 : OK

Verify CPU2 : OK

Restart UniFlash

Verify CPU2 : OK

Verify CPU1 : No meaningful verification, no console entry.

Verify CPU2 : OK

Verify CPU1 : No meaningful verification, no console entry.

Verify CPU2 : OK

Log Before Restart:

Log After Restart: