While using CCS 10.4.0.00006 under Windows to check the Cortex-R5 operation for a floating-point division by zero wanted to use the disassembly view to confirm the compiler had issued a floating-point divide instruction.

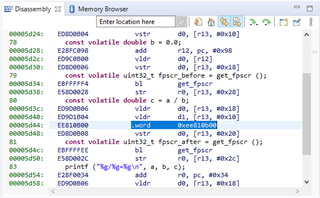

Noticed the CCS Disassembly View was displaying ".word 0xee810b00" and thus didn't recognise the instruction:

The Cortex-R5 is in ARM mode and changing the Disassembly Style from "Mixed ARM/Thumb" to "ARM Only" didn't make a difference.

Looking at the assembler listing saved by the compiler shows the expected VDIV.F64 instruction with the encoding of EE810B00:

170 .dwpsn file "../source/HL_sys_main.c",line 80,column 29,is_stmt,isa 2

171 00000030 ED9D0B06 VLDR.64 D0, [SP, #24] ; [DPU_V7R4_PIPE0] |80|

172 00000034 ED9D1B04 VLDR.64 D1, [SP, #16] ; [DPU_V7R4_PIPE0] |80|

173 00000038 EE810B00 VDIV.F64 D0, D1, D0 ; [DPU_V7R4_PIPE0] |80|

174 0000003c ED8D0B08 VSTR.64 D0, [SP, #32] ; [DPU_V7R4_PIPE0] |80|

The project used is attached.