Part Number: TM4C1294NCPDT

HI All,

I'm trying to place my entry point function at address 0x11000. Yet the linker consistently places it at 0x11001. I get no warnings or errors during linking.

If I jump to 0x11000 (desired address), the processor crashes.

If I jump to 0x11001, the program runs properly so it appears that my entry point function is really at 0x11001.

I've included as much info as I could find to demonstrate the contradictions.

Thank you,

Peter

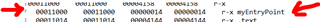

My linker file where I map my entry function to a section called 'myEntryPoint' and map it to address 0x11000.

SECTIONS

{

.intvecs: > 0x00010000

.text : > FLASH

.const : > FLASH

.cinit : > FLASH

.pinit : > FLASH

.init_array : > FLASH

.test : > FLASH

.vtable : > 0x20000000

.data : > SRAM

.bss : > SRAM

.sysmem : > SRAM

.stack : > SRAM

.nvv : > SRAM

myEntryPoint

{

entryPoint.obj(.text)

} > 0x11000

}

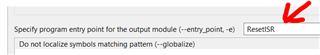

My linker configuration where I specify the name of my entry point, which is in the myEntryPoint.obj:

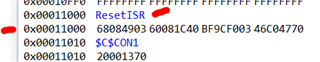

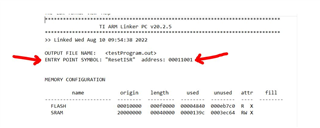

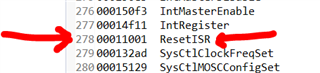

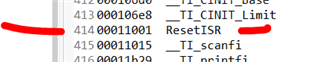

And sections of my map file, which has contradictory information as to the entry point:

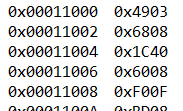

And finally, a snapshot of the actual memory after flashing the program via CCS: