Hello,

I'm using CCS 12 with F28379D and XDS110 probe.

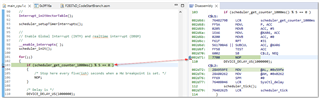

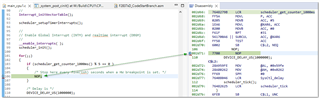

On other processors I have made frequent use of NOP + HW breakpoint to temporarily check that I am reaching certain branches of the program especially in highly optimization or inlined code.

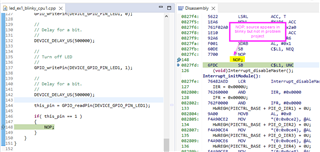

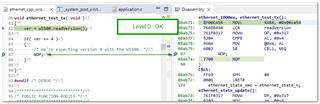

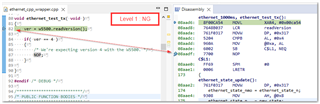

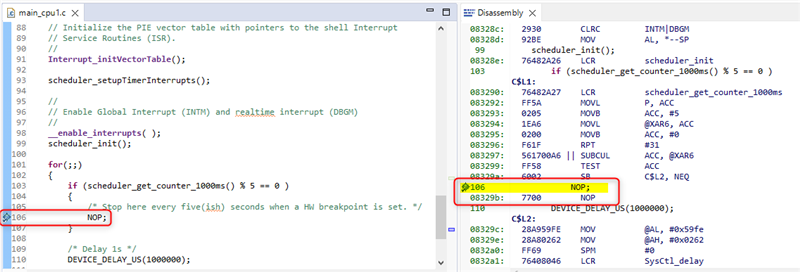

My problem is that in CCS, I cannot set a HW BP at a NOP even though the assembler reflects my source.

Furthermore setting a HW breakpoint at the NOP in the Dissassembly window stops the program at the wrong place. Please see the picture below.

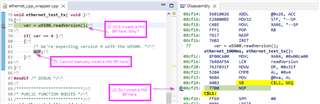

Can you please help to understand what's going wrong here? The assembler looks right but a BP at the NOP instruction at 0x8CF25 does not stop the program there.

Thank you very much.