Hi,

I would like to ask a question on FP alignment. I read probably contradictory statements on FP alignment from two sources:

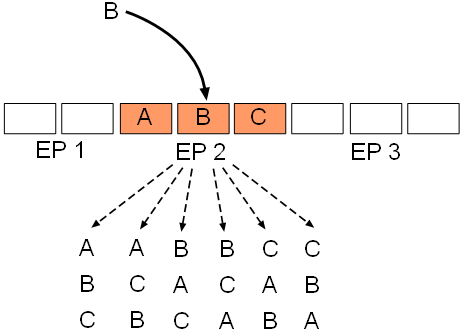

1. Page 132, SPRU732J, TMS320C64x-C64x+ DSP CPU and Instruction Set Reference Guide

Since the jump displacement address is left shifted by two bits first, I infer that the FP alignment should be 4 bytes = word based;

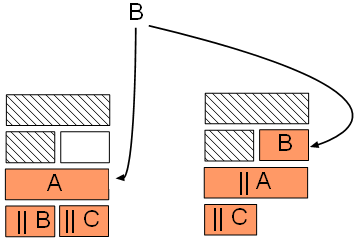

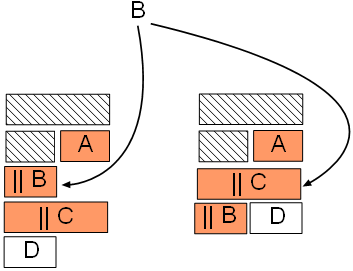

2. Slide 4/54 TMS320C64x+ Workshop

It is said FP are 256 bit = 8 word aligned.

So am I wrong here? What should be the right answer?

Zheng